И. Кривченко

С момента появления первого транзистора рынок постоянно выдвигает все новые требования к миниатюризации изделий микроэлектроники. Повышение степени интеграции полупроводниковых компонентов всегда ограничивалось не только возможностями технологии, но и архитектурными проблемами. Как сделать СБИС "универсальной", пригодной для большого числа потребителей, каждый из которых решает свою собственную задачу? Пути решения этой проблемы разделились.

С момента появления Первый путь применение программного способа управления. СБИС, предназначенные для обработки цифровых данных по заданной программе, получили название микропроцессоров. Второй путь выпуск ИС, аппаратный состав и назначение которых определяются конечным приложением микросхемами программируемой логики. И микропроцессоры, и микросхемы программируемой логики интенсивно развивались на протяжении последних лет. В настоящее время насчитывается несколько десятков различных семейств ИС из этой области: микропроцессоры, микроконтроллеры общего и целевого назначений, специализированные процессорные ядра для сложной обработки сигналов, микросхемы FPGA и CPLD.

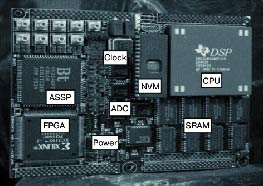

С момента появления Стратегической задачей микроэлектроники в настоящее время является создание микропроцессорной системы на кристалле. По существу, на площади одной кремниевой подложки требуется разместить не только тысячи или миллионы узлов базисной логики, но и процессорное ядро с набором разнообразных периферийных модулей, то есть, все то, что, например, находится на типовой системной плате (рис. 1). В самом общем случае она содержит процессор (это может быть DSP, микроконтроллер или микропроцессор) и ASSP-логику в виде Gate Arrays или ASIC. (ASSP Application Specific Standard Products заказные специализированные микросхемы массового применения, ориентированные на выполнение узкого класса задач. Классический пример чипсеты на материнских платах компьютеров, видеокартах и тому подобное). Кроме процессорного ядра и специализированной логики, на системной плате обычно находится программируемая логика в форме FPGA, CPLD или их комбинации. Далее, имеются блоки энергонезависимой и статической памяти, периферийные устройства, аналоговые узлы и модули управления питанием.

Рис. 1. Типовая системная плата

Какие же проблемы встанут перед заинтересованным пользователем, который захочет заказать себе систему на одном кристалле? Прежде всего, это значительные суммы так называемых невозвращаемых затрат (NRE) на подготовку производства маски. Далее, придется заплатить за инструментальные средства для разработки и поддержки проекта маски, а также для моделирования и верификации. В результате получается заказной кристалл с фиксированной архитектурой и большим сроком разработки, так что степень риска получить не совсем то, что ожидали, весьма высока. Если возникает необходимость внести даже незначительные изменения, то проект приходится переделывать с самого начала. И, наконец, по-следней встает проблема интеллектуальной собственности. Нужно найти поставщиков фиксированных ядер (процессор, различные типы памяти) и заплатить за эти ядра; нужно найти изготовителя конечного кристалла, который был бы способен интегрировать все выбранные системные узлы в пределах площади единого кремниевого кристалла. После всего этого необходимо пройти экспертизу и испытания новой микросхемы В общем, резюме неутешительное в настоящее время система на кристалле недоступна для большинства пользователей.

Мы расскажем о новом семействе изделий микроэлектроники FPSLIC, созданном корпорацией Atmel (США). Концепцию FPSLIC можно рассматривать как первый реальный шаг к слиянию двух путей развития сложных универсальных микросхем (микропроцессоров и программируемой логики) в единое целое.

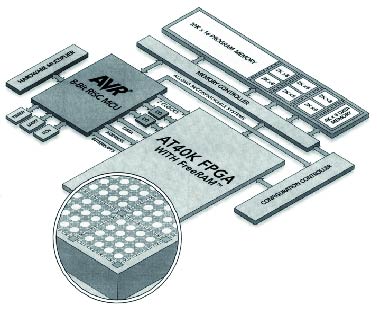

FPSLIC является аббревиатурой Field Programmable System Level Integration Circuits, что приблизительно может быть переведено как Программируемые Пользователем Микросхемы Системного Уровня Интеграции. FPSLIC спроектированы как семейство стандартных кристаллов, которое будет развиваться с течением времени. Первыми появятся микросхемы, базирующиеся на ядре AVR RISC микроконтроллеров Atmel. Блок-схема такого FPSLIC-устройства приведена на рис. 2.

Рис. 2. Общая структурная схема FPSLIC

Прежде всего, Atmel поместила на кристалл модуль стандартного FPGA семейства AT40K, обеспечив разработчику программируемую аппаратную платформу для реализации его собственных макросов и проектов непосредственно в FPSLIC. Рядом с блоком FPGA находится AVR-микроконтроллер. Здесь впервые стандартное ядро AVR выполняет команды из SRAM, что значительно повышает скорость его работы. Для обеспечения дополнительной эффективности при выполнении DSP-приложений к ядру AVR добавлен блок аппаратного умножения. Рядом с микроконтроллером размещен набор фиксированных периферийных узлов: два UART, три таймера-счетчика (два 8-разрядных и один 16-разрядный) и два порта ввода/вывода. Добавлен аппаратный интерфейс I2C, который позволяет AVR обмениваться данными с внешней конфигурационной EEPROM, используемой для программирования FPSLIC. Блок фиксированной логики, размещенный между AVR и FPGA, позволяет использовать массив FPGA для реализации дополнительных программируемых периферийных узлов в реальном проекте, причем эти новые периферийные устройства будут доступны в общем адресном пространстве памяти AVR.

Архитектура общего массива статической памяти SRAM внутри кристалла FPSLIC была реализована таким образом, чтобы обеспечить разработчику максимальную гибкость в распределении адресного пространства. Объем памяти программ составляет 10Кx16, памяти данных 4Кx8. Помимо этих фиксированных массивов памяти, на кристалле имеется дополнительный блок памяти 6Кx16, который может использоваться или как дополнительная память программ, или как дополнительная память данных, в зависимости от назначения приложения и желания разработчика. Если, например, приложение пишется на языке C, то нужна дополнительная память программ; если реализуется какой-либо алгоритм DSP, то обычно требуется дополнительная память данных. Конфигурация распределения памяти сохраняется в специальном регистре конфигурации системы, который находится в контроллере памяти FPSLIC. Регистр конфигурации загружается при включении питания вместе с SRAM программ, SRAM данных и FPGA из внешней конфигурационной EEPROM. Еще одной особенностью архитектуры является то, что AVR может непосредственно реконфигурировать FPGA на кристалле. Это обстоятельство является очень важным, учитывая требования постоянно развивающегося рынка портативных реконфигурируемых систем.

Выделим три главных преимущества FPSLIC, полученных в результате размещения ядра AVR, блока FPGA и массива статической памяти на одном кристалле.

Первое повышенная степень интеграции, новый качественный уровень конечного изделия. Энергопо-требление, по сравнению с вариантом системы, реализованном на дискретных компонентах, снизилось вдвое. Низкое энергопотребление FPSLIC предполагает его использование в разнообразной портативной аппаратуре.

Второе производительность. Ядро AVR, реализованное в составе FPSLIC по технологическому процессу SRAM/ASIC, способно работать с производительностью свыше 30 MIPS.

Третье значительное, революционное сокращение времени выхода на рынок новых проектов и разработок. Комбинируя аппаратный (FPGA) и программный (AVR) подходы к созданию сложных универсальных микросхем в пределах площади одного кремниевого кристалла, Atmel разработала также набор инструментальных средств поддержки разработок, которые позволяют разработчику проектировать и верифицировать как аппаратную, так и программную части проекта одновременно. Объединение стандартных узлов AVR и FPGA на одном кристалле позволяет непосредственно использовать в FPSLIC коды проектов, которые уже были реализованы на базе AVR или FPGA.

Первое семейство FPSLIC, содержащее AVR и FPGA, имеет обозначение AT94Кхх. В нем анонсированы три микросхемы с емкостью FPGA 40000, 20000 и 10000 эквивалентных вентилей AT94K40, AT94K20 и AT94K10, соответственно. Первым будет изготовлен кристалл AT94K40, ориентировочное время выпуска июнь 2000 года.

Рассмотрим реализованную архитектуру FPSLIC. AT94K это современное изделие микроэлектроники, представляющее в своей основе стандартную FPGA серии AT40K с интегрированным на кристалл блоком статической памяти SRAM и аппаратным ядром AVR-микроконтроллера. Архитектура FPGA сохранена здесь такой же, как и у микросхем версии AL семейства AT40K. Массив FPGA выполнен по технологическим нормам 0,35 мкм. Он имеет улучшенную структуру межсоединений, дополнительные регистры в элементах ввода/вывода, доступ к тактированию непосредственно из самой FPGA и распределенную скоростную двухпортовую оперативную память FreeRAMTM. Ло-гический элемент представляет собой восьмиугольную ячейку с 8 связями с 8 соседними ячейками. Массив FPGA имеет 8 глобальных линий тактирования. Шесть из них являются внешними, а две внутренними, причем их источником служит ядро AVR. Одна из внутренних линий тактирования соединена с системной тактовой шиной микроконтроллера, а другая может быть программным образом подключена к одному из восьми различных источников тактового сигнала, которые генерируются внутри AVR выходы таймеров/счетчиков, сторожевого таймера и так далее. Весь массив FPGA в FPSLIC динамически реконфигурируем, имеет хорошие показатели статического и динамического энергопотребления, что делает его пригодным для реализации мобильных приложений.

AVR RISC-микроконтроллер имеет в системе команд около 120 инструкций. Добавлен блок аппаратного умножения для поддержки проектов и подсистем, основанных на DSP. Ожидаемая производительность ядра AVR более 30 MIPS при тактовой частоте 40 МГц, что достигается за счет выборки команд из быстрой SRAM. Архитектура AVR оптимизирована для разработки приложений на языке C, имеется регистровый файл на 32 регистра. Микроконтроллер также поддерживает несколько режимов пониженного энергопотребления.

Для периферийных устройств, специфицируемых пользователем в массиве FPGA, реализована дополнительная поддержка. Микроконтроллер имеет возможность записывать информацию непосредственно в FPGA через механизм ввода/вывода со специализированным адресным пространством. Шина данных AVR также непосредственно соединена с массивом программируемой логики, так что имеется возможность получать доступ к адресуемому периферийному устройству в FPGA. В микроконтроллере аппаратно поддерживается 16 дополнительных векторов прерываний от FPGA. Все они распределены в общем пространстве векторов прерываний AVR с различными уровнями приоритета. Имеются также четыре отдельных внешних прерывания в AVR.

Микросхемы семейства AT94K допускают использование нескольких типов источников внешней опорной частоты. Напряжение питания составляет 3,3 В, так как FPSLIC изготавливаются по 0,35-мкм технологии. Новые микросхемы полностью совместимы по расположению и назначению внешних выводов с микросхемами FPGA семейств Atmel AT40K, Xilinx 4000, 5200 и SPARTAN и являются также PCI-совместимыми. Поэтому все средства поддержки разработок, уже разработанные и имеющиеся для FPGA, могут быть использованы и для работы с микросхемами FPSLIC. Это, например, комплект макетных плат ATDH40M и новый, недавно выпущенный набор разработчика ATSTK40.

Рассмотрим подробнее взаимодействие между FPGA и AVR в микросхемах семейства FPSLIC. Ядра FPGA и AVR связаны гибким интерфейсом, который позволяет реализовывать различные методы системной интеграции.

Рис. 3. Взаимодействие между AVR и FPGA в FPSLIC

AVR имеет прямой доступ к ресурсам FPGA. Шина данных микроконтроллера может быть напрямую подключена к глобальным шинам (Express Buses) ядра FPGA, которое при этом можно рассматривать как сложное периферийное устройство, отображенное на адресное пространство ввода/вывода микроконтроллера (рис. 3). Четыре разряда адреса микроконтроллера дешифрируются в 16 селектирующих сигналов, используемых для выбора ресурсов FPGA, к которым происходит обращение. Выбор направления передачи данных осуществляется AVR. Ядро FPGA может генерировать сигналы запросов прерывания для микроконтроллера по 16 линиям. Таким образом, каждое периферийное устройство, реализованное в FPGA и имеющее свой собственный адрес в пространстве ввода/вывода AVR, может иметь отдельное прерывание.

Рис. 4. Структура массива памяти в FPSLIC

На рис. 4 показана структура массива памяти в FPSLIC. Между ядрами FPGA и AVR расположено 36 Кбайт двухпортовой SRAM с временем доступа 15 нс. Эта SRAM используется, в основном, ядром AVR в качестве памяти программ и памяти данных. Однако, FPGA и AVR могут осуществлять разделенный доступ к этой памяти. Порт SRAM, подключенный к FPGA, используется при конфигурации кристалла FPSLIC для загрузки памяти программ и памяти данных микроконтроллера.

Внутренняя память программ и данных разделена на три блока: два фиксированных и один перемещаемый. Фиксированные блоки: память программ объемом 10Кx16 и память данных 4Кx8. Перемещаемый блок разделен на три банка, каждый из которых может переключаться между памятью программ и памятью данных. Переключение происходит от банка памяти программ 2Кx16 к банку памяти данных 4Кx8, и наоборот. Такое изменение организации памяти обусловлено тем, что память программ AVR имеет 16-разрядную организацию, а память данных 8-разрядную.

Рис. 5. Доступ к внутренней статической памяти в FPSLIC

На рис. 5 показана организация доступа к внутренней статической памяти. Как уже говорилось, FPGA и AVR могут осуществлять разделенный доступ к двухпортовой памяти данных независимо друг от друга. Это означает, что FPGA может записывать и считывать данные из SRAM в то же самое время, когда это делает AVR. Такая структура позволяет разработчику реализовать различные способы буферного обмена данными между FPGA и AVR: буферы типа LIFO, FIFO или другие. Порт данных SRAM, подключенный к FPGA, не имеет строба разрешения чтения данных. Подразумевается, что для FPGA чтение данных из SRAM всегда разрешено. Для предотвращения конфликтов при одновременном обращении обоих ядер к одному адресу ОЗУ разработчик должен обеспечить арбитраж, управляя приоритетами обращений к памяти. В большинстве случаев, для ограничения доступа к памяти от FPGA может быть использован специальный управляющий регистр микроконтроллера.

В FPSLIC реализована возможность создания динамически реконфигурируемой системы, поскольку FPGA имеет функцию Cache Logic и может быть перепрограммирована под управлением AVR непосредственно в процессе работы в рeжиме AVR Cache. Эта архитектурная особенность является пока уникальной в промышленности. Структура механизма конфигурации FPGA под управлением AVR приведена на рис. 6. Ядро AVR имеет доступ к конфигурационной памяти FPGA по записи. В адресном пространстве микроконтроллера имеются 4 ячейки памяти, которые используются для генерации 4-байт записи (24-разрядный адрес и собственно байт данных), необходимой для записи в FPGA. Фактически, в этом режиме FPGA рассматривается микроконтроллером как синхронное оперативное запоминающее устройство. Наличие такого режима позволяет изменять конфигурацию FPGA в системе алгоритмически, по ходу выполнения рабочей программы микроконтроллера. Выгоды этого очевидны. Можно, например, сохранить несколько вариантов конфигурации FPGA во внешней энергонезависимой памяти (например, DataFlash), а затем, по мере необходимости, переписывать их в AVR, переформатировать и загружать в FPGA. А поскольку программируемая логика пока существенно дороже энергонезависимой памяти, применение FPSLIC позволит конечным пользователям найти компромисс между логикой и памятью, сэкономить средства и получить дополнительные выгоды от гибкости, многофункциональности и энергопотребления конечных систем. Реконфигурируемые системы позволяют заметно снижать потребление энергии, что является сильным аргументом в защиту использования технологии FPSLIC на рынке портативных и носимых интеллектуальных устройств.

Рис. 6. Конфигурация массива FPGA в микросхеме FPSLIC под управлением AVR

Краткий обзор аппаратной части был бы бесполезен без дополнительной информации о программных средствах поддержки разработок для FPSLIC. Очевидно, что эффективность освоения новых аппаратных решений гораздо выше, если средства поддержки разработок для них уже знакомы разработчикам. Поэтому Atmel поддерживает дальнейшее развитие и совершенствование уже существующих программных пакетов как для FPGA, так и для AVR. Создан объединенный набор средств поддержки разработок, который действительно реально поможет семейству FPSLIC увидеть свет. Для поддержки FPSLIC используется уже существующее, "обкатанное" программное обеспечение. Средства программной разработки и поддержки для FPGA фирмы Atmel активно используются и совершенствуются на протяжении 6 лет, а инструментальные средства для AVR-микроконтроллеров 3 года. Atmel выходит на рынок с законченными программными средствами поддержки, которые дают разработчику полноценный доступ к обеим составляющим внутренней структуры FPSLIC и возможность наблюдать за процессами, происходящими в системе. Программная среда для работы с FPSLIC работает в среде Windows 98/2000/NT. Это предписывает разработчикам использование в работе только современных Windows-ориентированных платформ. Требования к системным ресурсам для платформы PC: Pentium 300 МГц и 128 Мбайт оперативной памяти.

Попробуем представить процесс создания сложной заказной микросхемы. Пусть некто создал сложный проект на FPGA, CPLD или Gate Arrays, и объявил, что разработка запускается в производство. Но затем проходит несколько томительных месяцев и, наконец, появляется конечная продукция. Длительная задержка (иногда до года!) обусловлена тем, что реализация аппаратной части проекта в целом завершается в начальной стадии его создания, а программной части существенно позже. Поэтому имеет место последовательный процесс сначала разработка аппаратной части и только затем разработка программных средств поддержки проекта. И зачастую случается, что спустя несколько месяцев программисты приходят к выводу, что либо они не могут заставить проект работать достаточно быстро в программном обеспечении, либо он потребляет слишком много энергии, либо что-нибудь еще. Затем программисты требуют у разработчиков аппаратной части выполнить тот или иной ряд переделок. То есть, начинается следующая итерация процесса. В конце концов, все нестыковки устраняются и выпускается промышленный образец.

Естественным выходом из этой ситуации явилось бы использование средств поддержки, которые позволяли бы проводить одновременную разработку как аппаратной, так и программной частей проекта. И так как Atmel впервые размещает FPGA и процессор на одном кристалле, то он позаботился и о том, чтобы снабдить FPSLIC именно такими средствами совместной разработки. Atmel планирует обеспечить пользователя возможностью находить компромиссы взаимодействия аппаратной и программной частей уже в самом начале проекта, чтобы конечное изделие не проходило бы многократный итерационный процесс разработки и отладки, традиционный для заказных микросхем. Причем основной особеностью является доступность новых средств поддержки разработок для широкого круга конечных пользователей.

Средства совместной разработки проектов для FPSLIC включают в себя набор инструментальных средств и программных приложений как для AVR, так и для FPGA. Общее название для нового программного продукта System Designer. По существу, это многооконная структура с удобным пользовательским интерфейсом, которая позволяет использовать совместно многочисленные программные инструментальные пакеты. Отметим, что в настоящее время System Designer содержит средства поддержки разработок для FPGA и AVR. Планируется, что в дальнейшем средства совместной разработки проектов для FPSLIC будут поддерживать как другие микропроцессорные ядра (например, ARM), так и возможные новые технологические реализации программируемой логики, если вдруг захочется заменить архитектуру AT40K на более совершенную.

Что касается средств поддержки разработок для AVR, то здесь все достаточно просто. Последняя серия программного продукта AVR Studio версий 3.хх интегрирована (с некоторыми незначительными модификациями) в System Designer. Для другой аппаратной половины FPSLIC массива FPGA ситуация немного сложнее.

Набор аппаратных и программных средств поддержки разработок для ядра FPGA, известный как Figaro Integrated Design System (IDS), достаточно хорошо изучен разработчиками. В нем поддерживается языковый ввод проектов через пакет HDLPlanner (с использованием языков описания аппаратуры VHDL и Verilog) и HDL-синтез как часть основного набора инструментальных средств. Но, в отличие от Figaro IDS, в состав пакета System Designer включен синтезатор фирмы Exemplar Logic (подразделение Mentor Grafics) как стандартное программное средство синтеза HDL. Однако, пользователи могут использовать и другие синтезаторы по их желанию, например, Synplify фирмы Synplicity или FPGA Express фирмы Synopsys, которые могут быть легко интегрированы в System Designer. После этапа синтеза языкового описания проекта происходит его автоматическое размещение в выбранном кристалле и последующая разводка внутренних межсоединений. При этом пользователь имеет возможность вручную корректировать результаты размещения и разводки. Процесс завершается генерированием bitstream-файла, который используется для конфигурирования ядра FPGA.

Весь процесс проектирования должен проходить через совместную разработку и аппаратной, и программной частей всего устройства в целом. Важной особенностью пакета System Designer является возможность программной симуляции и анализа взаимодействия аппаратных средств (ядра FPGA) и программного обеспечения (ядра AVR). Любые ошибки, выявленные в ходе программной симуляции, могут быть быстро исправлены, что значительно сокращает общее время разработки.

Рис. 7. Две среды моделирования в System Designer

Посмотрим на пакет System Designer немного подробнее: какие части он содержит и какие выгоды дает разработчику. На рис. 7 показано, из каких частей состоит System Designer. В него включены две среды моделирования: программного кода AVR и аппаратуры, реализованной в массиве FPGA. Среда моделирования программного кода AVR, по сути, представляет собой отладчик AVR Studio. При этом разработчик получает все преимущества последнего, например, такие сервисные функции, как "пошаговое исполнение программы", "выполнение программы до точки останова", "вход в подпрограмму", "выполнение без входа в подпрограмму" и так далее. Среда моделирования FPGA представляет собой симулятор языкового описания аппаратуры. Atmel включил в состав System Designer симулятор ModelSim фирмы Model Technology (подразделение Mentor Grafics), получив при этом самые современные возможности моделирования аппаратуры.

Для анализа взаимодействия аппаратуры и программного кода необходимо соединить системы моделирования AVR и FPGA. Такая связь между обеими системами реализована в System Designer с помощью операционной среды совместной разработки и верификации. Эта операционная среда скрыта от пользователя, но позволяет двум средствам поддержки разработок AVR Studio и ModelSim взаимодействовать друг с другом. Например, если микроконтроллер записывает данные по одному из адресов FPGA в программном симуляторе, то в окне ModelSim сразу же виден результат этой записи. Или, например, если аппаратура FPGA активирует одну из линий прерывания микроконтроллера, то программный симулятор AVR Studio выполнит переход на подпрограмму обработки инициируемого прерывания.

Связав две среды моделирования вместе, Atmel обеспечил полное взаимодействие потоков программного моделирования на любом шаге в процессе проектирования для FPSLIC. Разработчик может наблюдать в деталях за взаимодействием аппаратной логики и программного кода. В результате получен чрезвычайно мощный инструмент, позволяющий значительно сократить время проектирования, отладки и выпуска готовой продукции на рынок. Дополнительным преимуществом является отсутствие необходимости применения внутрисхемного эмулятора реального времени.

Рис. 8. Состав программного пакета System Designer

System Designer представляет собой гибкий программный инструмент, обладающий средствами ввода проекта, его синтеза, автоматического размещения и трассировки, моделирования а также генерацией загрузочного bitstream-файла (рис. 8). Это производительный и мощный пакет с многооконной структурой, позволяющий разработчику свободно ориентироваться в различных частях проекта, быстро и удобно переключаться между различными программными средствами. Средства совместной разработки и верификации пакета System Designer поддерживают проектирование системы в целом. System Designer позволяет различным языкам описания аппаратуры (VHDL, Verilog) моделироваться совместно с микропроцессорным программным обеспечением (языки C, C++, ассемблер) в единой программной среде. Это, в свою очередь, позволяет значительно (от 10 до 100 раз) сократить период времени между началом разработки и выходом готового изделия на рынок.

Перечислим ключевые особенности System Designer:

- возможность просмотра на этапе проектирования как исходного текста, так и ассемблерного кода;

- возможность просмотра массивов внутренней памяти и регистров FPSLIC;

- возможность поэтапной симуляции разрабатываемого проекта.

Поэтапная симуляция проекта заключается в следующем. Сначала на языке описания аппаратуры создается поведенческая модель разрабатываемого устройства. Производя симуляцию поведенческой модели, разработчик может отлаживать алгоритм функ-ционирования всего устройства в целом. Затем, после этапа синтеза и размещения проекта, разработчик получает back-annotation-файлы, содержащие языковое описание аппаратуры, реализованной в ядре FPGA. Эти файлы, совместно с циклически точной моделью микроконтроллера, используются для окончательной симуляции разрабатываемого устройства, размещенного в выбранном типе кристалла. Окончательная симуляция происходит не на уровне поведения, а на уровне аппаратуры. При этом возможна отладка каждого из блоков устройства в отдельности.

Рассмотрим аспекты конфигурации FPSLIC. Программирование микросхем FPSLIC практически идентично конфигурированию стандартных микросхем FPGA при помощи последовательной конфигурационной памяти. Необходимый объем памяти для конфигурации определяется логической емкостью массива FPGA плюс размер блока SRAM, используемой в качестве памяти команд для ядра AVR плюс несколько дополнительных битов, требуемых для конфигурации (рис. 9). Так, AT94K10, самое маленькое устройство с 10К эквивалентными вентилями в блоке FPGA, требует для конфигурации 423 Кбит, что перекрывает емкость конфигуратора AT17C512. Для AT94K20 потребуется уже 524 Кбит, а для AT94K40 809, что в обоих случаях перекрывается конфигуратором емкостью 1 Мбит (AT17C010). Фактически, приведенные выше требования к объему памяти конфигураторов можно снизить, используя при генерации bitstream-файла опцию сжатия.

Рис. 9. Объем конфигурационной памяти для FPSLIC

Существует еще одна важная особенность, которую следует упомянуть. Размещение аппаратного блока интерфейса I2C в ядре AVR позволяет разработчику не только программировать конфигурационную память под управлением AVR (если это требуется), но также использовать свободные ячейки внутри нее как дополнительную системную EEPROM. Очень удобным оказывается использование незадействованных битов в массиве конфигурационной памяти для хранения или модификации разнообразных энергонезависимых данных, увеличивая тем самым системные ресурсы.

Итак, что же такое FPSLIC? FPSLIC это:

- системное решение в пределах площади единого кремниевого кристалла, полностью программируемое самим пользователем. Преимущества низкое энергопотребление, экономия площади печатной платы и повышенная надежность системы в целом;

- объединение стандартной FPGA AT40K, выполненной по технологии SRAM, и высокоэффективного ядра AVR RISC, память программ которого также реализована по технологии SRAM. Логическая емкость FPGA может варьироваться от 10000 до 40000 эквивалентных вентилей, при этом сохраняется возможность иметь свободную распределенную оперативную память FreeRAM в FPGA;

- новая возможность совместной верификации проекта на протяжении всего цикла разработки. Совместная верификация позволяет осуществлять проектирование аппаратной части, программного обеспечения и печатной платы проекта одновременно;

- совместимые по выводам микросхемы с уже имеющимися семействами программируемой логики Atmel AT40K, Xilinx 4000, 5200 и Spartan, размещенными в однотипных корпусах;

- возможность проводить модификации проектов в уже готовых конечных устройствах. Так как в основе внутренней структуры FPSLIC лежит ячейка SRAM, то они могут быть модифицированы путем удаленного доступа в "полевых условиях", через модем или даже через Интернет;

- полная совместимость для уже существующих проектов на AVR и FPGA семейства AT40K. Любой программный код, любой аппаратный проект, однажды уже сделанный для микроконтроллера или FPGA, может быть непосредственно интегрирован в среду проекта на FPSLIC;

- отсутствие необходимости в применении внутрисхемного эмулятора на этапе отладки проекта в целом благодаря возможности совместной верификации;

- стандартное семейство микросхем. Для потребителей продукции класса ASIC открывается путь дальнейшего снижения стоимости конечных изделий при полном сохранении возможности их последующей реконфигурации, модификации и даже переориентации без дополнительных капиталовложений и ограничений, связанных с минимальным необходимым количеством микросхем для заказа изделия класса ASIC. Минимальных требований к объему заказа для FPSLIC не существует.

В заключение подчеркнем, что микросхемы системного уровня интеграции это качественно новый продукт. FPSLIC не следует рассматривать как только микроконтроллер с программируемой пользователем перифе-рией. Это "не проходит" ни с функциональной (слишком ограниченное восприятие новых качественных возможностей), ни с экономической точек зрения (неоправданно высокая стоимость кристалла для микроконтроллера с богатой периферией). Если действительно необходимо иметь лишь микроконтроллер с развитыми периферийными возможностями, то вполне подойдет, например, кристалл ATmega103. Или можно применить дешевое процессорное ядро типа 80C31, 68HC05/11, 80С196 и т.п., добавив к нему специализированную микросхему программируемой пользователем памяти и периферии, выпускаемой фирмой WSI. Данное различие более чем существенно, и его обязательно следует иметь в виду, чтобы выбрать наиболее подходящий кристалл для реализации конкретной задачи.

В следующем номере "Chip News" мы вернемся к FPSLIC и расскажем о семинаре Atmel, посвященном этой теме.

E-mail: igor@efo.spb.ru

Системная интеграция в микроэлектронике FPSLIC

Системная интеграция в микроэлектронике FPSLIC