В. Шахнов, А. Власов, А. Кузнецов, Ю.Поляков

АОЗТ 'Инструментальные системы' [6] выпускает на сегодня в России самую широкую номеклатуру различных многофункциональных мультипроцессорных плат, как в виде 'виртуальных' устройств, так и в виде крейтовых модулей и полнофункциональных вычислителей. Элементной базой высокопараллельных нейроускорителей данной фирмы являются DSP фирмы Analog Devices (SISD Sharc, SIMD Sharc, Static Superscalar Sharc) и DSP фирмы Texas Instrumens (в основном, семейств TMS320C4x, TMS320C6xxx). Интерфейсы выпускаемых модулей различны: ISA, PCI, CompactPCI, VME, IEEE1394, RS232, RS482, RS485 и др. Спектр заказных изделий практически неограничен. Проанализируем ряд серийно выпускаемых высокопараллельных ускорителей фирмы 'Инструментальные системы' на конкретных примерах.

Плата ADP160PCI

Плата является наиболее ярким представителем параллельных виртуальных вычислителей и предназначена для построения систем радиосвязи, радиолокации, гидролокации, вибродиагностики, обработки изображений. Она построена на базе 32-разрядного 600 Mflops процессора SHARC2 компании Analog Devices. Cигнальный процессор ADSP-21160 работает на тактовой частоте 100 MГц, имеет два исполнительных устройства для выполнения SIMD-операций и внутреннюю память 4 Мбит. 64-разрядная шина процессора обеспечивает одновременную выборку двух 32-разрядных данных для их параллельной обработки в процессоре. Процессор обеспечивает вычисление 1024-точечного комплексного преобразования Фурье с битреверсными перестановками за 90 мкс.

Плата ADP160PCI устанавливается в PCI-шину персонального компьютера (ПК) и позволяет выполнять программы во взаимодействии с АЦП и ЦАП, размещёнными на дочерней расширительной плате ADM. При этом имеется возможность загружать программы ADSP-21160 и данные, осуществлять сброс процессора, просматривать память и инициировать выполнение программы. Для отладки программного обеспечения в среде VisualDSP к плате ADP160PC подключается внутрисхемный эмулятор EZ-ICE. Он позволяет загружать программы, начинать и останавливать их выполнение, наблюдать и изменять состояние регистров и памяти, выполнять другие операции отладки.

Плата ADP160PCI содержит процессор ADSP-21160 и одно место для установки дочерней платы ADM. Объём синхронной динамической памяти составляет от 32 до 128 Мбайт. Микросхема 32-разрядного моста 'шина PCI - локальная шина' обеспечивает доступ персонального компьютера к HOST-порту и внутренней памяти процессора ADSP-21160 и доступ процессора ADSP-21160 к памяти и портам персонального компьютера. Плата ADP160PCI обеспечивает режим мастера шины в соответствии со спецификацией PCI версии 2.2. Многочисленные режимы синхронизации и прерываний, в том числе, и по спецификации ISO, обеспечиваются посредстом регегистров mailbox и doorbell. Шесть линков процессора ADSP-21160 обеспечивают высокоскоростной (100 Мбайт/с) бесконфликтный обмен как c процессорами SHARC_2, так и с процессорами SHARC. Тем самым обеспечивается возможность построения масштабируемых многопроцессорных систем на процессорах семейства ADSP-21160 и ADSP-21060/62. На плате ADP160PCI все линки процессора ADSP-21160 выведены на разъёмы, обеспечивая объединение с другими процессорными платами для наращивания вычислительной мощности.

Блок-схема платы ADP160PCI представлена на рис. 1. Обращения к процессору ADSP-21160 осуществляются по интерфейсу шины PCI. Так как интерфейс PCI непосредственно связан с Ноst-портом процессора, персональный компьютер получает доступ к его внутренним ресурсам. Пропускная способность моста при записи из персонального компьютера во внутреннюю память процессора ADSP-21160 составляет 15 Мбайт/с, при чтении персональным компьютером из внутренней памяти процессора ADSP21160 - 10 Мбайт/с. Чтобы разгрузить процессоры от рутинной работы по пересылке массивов, в микросхему моста встроены два контроллера прямого доступа к памяти, обеспечивающие пересылку данных между памятью персонального компьютера и внутренней памятью процессора ADSP-21160 со скоростью до 40 Мбайт/с.

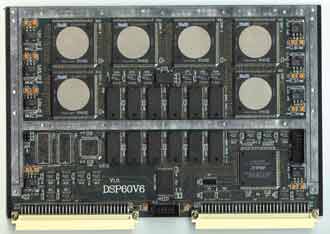

DSP60V6

DSP60V6 - плата высокопроизводительного мультипроцессорного модуля сбора и цифровой обработки сигналов, основанная на процессоре цифровой обработки сигналов ADSP-21060/62 SHARC (рис. 2). Она позволяет выполнять программы SHARC во взаимодействии с устройствами, размещёнными на дочерней плате ADM, в качестве которой могут использоваться модули АЦП, ЦАП. ADP60V5 устанавливается в промышленные крейты с размером плат 6U.

Модуль может работать как автономно, так и с компьютером, имеющим шину VME. Вы можете загружать программы ADSP-21060/62 и данные через шину VME и/или через пользовательские выводы разъёма J2/P2 (X2), осуществлять сброс процессоров, просматривать память и инициировать выполнение программ.

Модуль имеет в своём составе процессорный кластер из шести процессоров ADSP2106x производительностью 120 MFLOPs каждый. В процессорном кластере устанавливается до 1М?48 бит оперативной статичекой памяти и до 16М?32 бит оперативной динамической памяти. Кластер имеет в своём адресном пространстве VME-интерфейс и FLASH-память 4М?8 бит. Модуль может работать независимо от шины VME, в этом случае приём и передача данных производится по 6 коммуникационным портам.

ADP44PCI

Несущий процессорный модуль ADP44PCI ориентирован на цифровую обработку сигналов и может быть легко конфигурирован для решения конкретных задач путём загрузки в модуль прикладного программного обеспечения и, в случае необходимости, подключения высокоскоростного субмодуля аналогового ввода/вывода и/или модуля стандарта TIM-40. Несколько ADP44PCI образуют распределённую вычислительную структуру из процессорных модулей, соединённых между собой с помощью высокоскоростных коммуникационных портов. В состав вычислительной структуры входят высокоскоростные устройства аналогового ввода/вывода, процессоры, локальная и глобальная память, интерфейсы ПЭВМ (рис. 3).

Процессорный несущий модуль ADP44PCI использует параллельный 32-разрядный ЦПОС с плавающей точкой TMS320C44 фирмы Texas Instruments. Четыре 30-Мбайт/с коммуникационных порта и канала ПДП процессора обеспечивают разнообразные возможности высокоскоростного обмена. Две шины TMS320С44 обеспечивают обмен 120 Мбайт/с каждая. Работая совместно, но независимо, процессор и ПДП TMS320С44 обеспечивают параллельный обмен данными со скоростью до 560 Мбайт/с. Высокоскоростные порты позволяют объединять процессоры в кольца, деревья, гиперкуб и так далее.

Процессорный несущий модуль ADP44PCI удовлетворяет стандарту TIM-40 и выполнен с использованием программируемых логических интегральных схем фирм Xilinx и Altera, реализующих функции обмена, средства управления процессором, прерываниями и каналами ПДП. Процессор TMS320C44 имеет производительность 60 МFlops. Объём статической памяти составляет от 128К?32 до 512К?32 на двух шинах процессора, предусмотрено расширение путём установки модулей SIMM динамической памяти до 16М?32 на глобальной шине процессора. Собственно кристалл TMS320С44 имеет 8 Кбайт встроенной памяти. На глобальной шине размещён интерфейс ADM-Connect для связи с субмодулем аналогового ввода/вывода со скоростью до 100 Мбайт/с.

Микросхема JTAG-контроллера, размещённая на плате, обеспечивает возможность загрузки и отладки задач ЦОС под управлением многооконного отладчика XDS510 фирмы Texas Instruments. Загрузка программ и данных, обмен информацией между TMS320C44 и ПЭВМ обеспечиваются через высокоскоростной коммуникационный порт. Система прерываний модуля обеспечивает выставление и обработку прерываний, запросов ПДП к TMS320С44 при обмене информацией с ведущей ПЭВМ. Ведущая ПЭВМ имеет возможность остановить, прервать TMS320С44, подтвердить обмен. Интерфейс коммуникационного порта включает FIFO ёмкостью 1 Кбайт в каждом направлении. Каждый процессорный узел имеет конфигурационный IDROM в соответствии со стандартом TIM-40.

Промышленный стандарт TIM-40 разработан консорциумом под руководством фирмы Texas Instruments для модулей на C40 и C44. Спецификация определяет аппаратные ресурсы, способы программирования и организации многопроцессорных систем. Процессорный несущий модуль ADP44PCI удовлетворяет основным требованиям стандарта TIM-40, что позволяет организовывать многопроцессорные системы с другими модулями стандарта TIM-40.

Важными составляющими модуля стандарта TIM-40 являются каналы связи с ведущей ПЭВМ, межпроцессорного обмена по коммуникационным портам, описание доступных С40 ресурсов в специальном идентификационном ПЗУ IDROM, порядок загрузки исполняемых программ, габариты и порядок подсоединения TIM-40 модулей.

Внутренняя структура интерфейса ПЭВМ модуля ADP44PCI полностью определяется загруженной конфигурацией ПЛИС. Реализация иной внутренней структуры системы для решения специальных задач пользователя возможна по отдельному заказу.

Модули на базе ТMS320C6701

Модули данного семейства ориентированы на применение в телекоммуникационных системах, включая базовые станции, системы медицинской диагностики, навигационные системы и системы позиционирования, мультимедиа и т.п., где требуется свервысокая вычислительная мощность. Мультипроцессорная плата на базе ТMS320C6701 показана на рис. 4.

Модуль ADP6701PCI фирмы 'Инструментальные системы' построен на базе микропроцессора TMS320C6701, обладающего производительностью 1 GFLOPS, и имеет в своём составе 8 параллельных вычислительных блоков. Он обеспечивает выполнение БПФ на 1024 отсчёта за 109 мкс.

Отличительными особенностями платы являются: буферная память тракта ввода 64K?32, вывода 64К?16, двухпортовая статическая память 64К?32, синхронная динамическая память до 16 Мбайт. Благодаря гибкому аппаратному интерфейсу на ПЛИС, обеспечивается программная совместиость различных субмодулей.

Нейроускорители НТЦ 'Модуль'

За период с 1989 по 1999 гг. в НТЦ 'Модуль' разработан ряд образцов нейрокомпьютерных вычислительных систем на современной элементной базе ведущих зарубежных фирм и на основе нейропроцессоров NeuroMatrix 6403 и 6404, созданного в НТЦ 'Модуль' [4]. Среди широкой линейки различных ускорителей можно выделить: нейроускорители на основе универсальных сигнальных процессоров (в основном, используется TMS320C4x) и нейроускорители на базе специализированного нейросигнального процессора NeuroMatrix, созданного в НТЦ 'Модуль'. Примерами ускорителей первого типа являются ускорительные платы М1и М2.

Ускорительная плата Ml

М1 выполнена на цифровых сигнальных процессорах TMS320C40 фирмы TEXAS INSTRUMENTS, связанных по высокоскоростным линкам. Имеется возможность каскадирования - подключения по линкам аналогичных плат. Структурная схема платы представлена на рис. 5.

Основные характеристики:

- ISA-интерфейс;

- до четырёх TMS320C40 с частотой 50 МГц;

- пиковая производительность - 100 MIPS, 200MFLOPS, 1100 MOPS;

- объём SRAM - 5 Мб (по 1 Мб на процессор + 1 Мб разделяемый с IBM PC), время выборки - 20 нс;

- объём DRAM - до 32 Мб;

- 8 внешних связей (скорость - 20 Мб/с).

Ускорительная плата М2

Многопроцессорный модуль М2 цифровой обработки сигналов выполнен на цифровых сигнальных процессорах TMS320C40 фирмы Texas Instruments и представляет собой одноплатную многопроцессорную вычислительную машину. Модуль предназначен как для автономной работы, так и для функционирования в составе ПЭВМ с системной шиной VMEbus, в том числе состоящей из нескольких таких же модулей. Конструктивно блок выполнен в соответствии с механическим стандартом VMEbus IEEE 1014 (6U).

Модуль М2 содержит:

- VME-bus контроллер;

- master/slave интерфейс;

- до шести TMS320C40 с частотой 50 МГц;

- до 2 Мб SRAM на процессор;

- до 64 Мб DRAM на плате;

- FLASH EEPROM до 0,5 Мб;

- 6 внешних связей (скорость - 20 Мб/с);

- JTAG-интерфейс;

- RS-232-интерфейс;

- общая производительность - до 300 MFLOPS.

Структурная схема ускорителя М2 приведена на рис. 6.

Нейроускорители на базе нейрочипов

Кроме нейроускорителей на базе

ПЛИС и DSP, в последнее время всё большее распространение находят

нейроускорители на базе специализированных нейросигнальных и нейросетевых

процессоров. Проанализируем особенности их реализации на конкретных примерах.

Двухпроцессорный встраиваемый модуль МЦ4.01 (NM1)

Встраиваемый модуль цифровой обработки сигналов МЦ4.01 (NM1) производства НТЦ 'Модуль' [4] предназначен для решения различных задач нейронными и нейроподобными алгоритмами, а также задач цифровой обработки сигналов и ускорения векторно-матричных вычислений (рис. 7). Модуль выполнен на спроектированных и разработанных в НТЦ цифровых сигнальных процессорах NeuroMatrixR NM6403 и представляет собой одноплатный нейроускоритель. Конструктивно выполнен в виде платы, вставляемой в стандартный слот шины PCI.

Нейроускоритель содержит:

- 2 нейропроцессора NM6403;

- от 2 до 8 Мбайт статической памяти (SRAM);

- 64 Мбайт динамической памяти (EDO DRAM);

- 4 внешних ком. порта с темпом обмена 20 Мбайт/с каждый.

Производительность:

- векторные операции - 1,9 млрд. операций с байтовыми операндами в секунду;

- скалярные операции - до 320 млн. операций в секунду.

Конструктивное выполнение: стандарт PCI (версия 2-1) с темпом обмена до 132 Мбайт/с.

Нейроускоритель МЦ4.02 содержит один процессор NM6403 и обладает масштабируемой производительностью от 40 до 11500 ММАС, обеспечивает обработку данных переменной разрядности от 1 до 64 бит. Модуль предназначен для работы в составе комплекса с системной шиной PCI, блок статической памяти модуля доступен для записи и чтения как со стороны процессора, так и со стороны шины PCI. На внешние разъёмы модуля выведены два комуникационных порта, аппаратно совестимых с портами TMS320C4x. Соединение коммуникационных портов нескольких модулей позволяет создавать мультипроцессорные системы различной конфигурации. Сейчас ведутся разработки по созданию модулей на базе процессора NM6404.

Нейровычислители Synapse

Компания Siemens Nixdorf Infor-mationssysteme (SNI) - дочернее предприятие концерна Siemens в сотрудничестве с Маннгеймским университетом создала нейрокомпьютер под названием Synapse 1, который появился на рынке в середине 1994 г., в дальнейшем были выпущены нейроускорители Synapse 2 и Synapse 3. Таким образом, SNI стала первой европейской фирмой, выпустившей нейрокомпьютеры. В настоящее время нейроускорители распространяются французской фирмой Tiga Technologies (gouimenou.tiga@wanadoo.fr).

Сфера применения нейромодулей - распознавание речи, изображений, образов, ускорение работы программных эмуляторов. Сложность моделирования на рабочей станции процесса самообучения для нейронных сетей до сих пор тормозила разработку нейронных применений, поскольку каждый шаг в обучении требует много времени. Что касается Synapse, то за один час самообучения он достигает таких же результатов, что и нейронные сети в обычном компьютере за целый год.

Эти системы обладают скалярной многопроцессорной архитектурой и наращиваемой памятью.

В состав Synapse 2 входят: один нейрочип МА16 (40 Гц), управляющий сигнальный процессор TMS320C50 (55 МГц), модуль целочисленной обработки на базе TMS320C50 (55 МГц), память образцов (Y-memory) и память весов (W-memory). Структурная схема нейроускорителя Synaps 2 представлена на рис. 8.

Серийно выпускаемые нейроускорители Synapse 3 поставляются с двумя процессорами МА 16. Пиковая эффективность одной нейроплаты Synapse 3 - 2,4 млрд.оп./с. Программное обеспечение работает в среде UNIX/XWIND и реализовано на C++. Нейронная сеть тоже описывается на С++ или может вводиться интерактивно с помощью графического интерфейса типа OSF/Motif, что позволяет визуализировать конфигурацию СБИС после отображения на неё структуры сети. Средства тестирования и эмуляции развиты очень хорошо.

Сравнительная диаграмма производительности нейроплат и Pentium200 на матричных операциях приведена на рис. 9.

Нейроплата CNAPS/PC-128 фирмы Adaptive Solutions

Плата CNAPS/PC была анонсирована в США в ноябре 1995 года. Она обладает рядом характеристик, которые на первый взгляд кажутся фантастическими. При обучении на сложных данных нейроплата превосходит ПК на базе Pentium по быстродействию в несколько сотен раз (на отдельных тестах - до 1000). Нейроплата позволяет прогнозировать заведомо 'гиблые' задачи - текущую ситуацию на мировом валютном рынке, динамику политических событий в регионах и даже исход футбольных матчей.

Старшая модель семейства имеет пиковое быстродействие 2,27 млрд.соединений/с, что позволяет сократить время аналитической обработки данных. Для сравнения: при решении нейросетевых задач стандартные персональные компьютеры показывают следующее быстродействие:

- 486 / 50 MГц - 750 тыс.соед./с;

- Pentium / 90 MГц - 1980 тыс.соед./с.

Конструктивно нейроплата CNAPS/PC представляет собой полноразмерную плату, вставляемую в слот расширения PC (поддерживаются шины ISA и PCI). На плате размещены 2 либо 4 нейроБИС, реализующие 64 либо 128 нейропроцессоров, соответственно. Кроме того, плата содержит 512 Кбайт быстродействующей кэш-памяти и стандартный SIMM ОЗУ - 4 Мб (может быть расширен до 36 Мб).

Нейроускорители фиРМы IBM

ISA ускоритель с 16 x ZISC 036

ZISC/ISA предназначен для IBM PC совместимых компьютеров. Ускоритель построен на 16 ZISC036 процессорах и имеет 576 нейронов. Возможна установка нескольких карт, одна из которых работает в режиме Master, а другие - в Slave.

PCI ускоритель на ZISC 036

IBM PCI ZISC ускоритель - высокопроизводительный нейровычислитель, предназначенный для работы в PCI-слоте:

- рабочая частота - 33 MГц;

- производительность - 165000 оп./с.

Ускоритель может содержать 1, 7, 13 или 19 ZISC036.

Нейрокомпьютеры

Рассматривая подходы к аппаратной реализации нейровычислителей, необходио отметить, что несмотря на широкое распространение различных высокопараллельных ускорителей для различных задач, число моделей полнофункциональных нейрокомпьютеров невелико. Коммерчески доступны только немногие, так как большинство из них реализованы для спецприменений. Наиболее яркими примерами нейрокомпьютеров являются [1,2]: нейрокомпьютер Synapse 1 (Siemens, Герания), нейрокомпьютер 'Силиконовый мозг' (созданный в США по программе 'Электронный мозг', предназначен для обработки аэрокосмических изображений, производительность 80 Пфлоп (80?1015 операций в секунду, объём равен объёму мозга человека, потребляемая мощность - 20 Вт), нейрокомпьютер 'Эмбрион' (Россия).

SYNAPSE-1

Базовый комплект SYNAPSE1-N110 (рис. 10) предполагает наличие главной ЭВМ - рабочей станции SUN SPARCSTATION 5 модели ТХ1 в качестве вспомогательного консолидирующего устройства, облегчающего процессы программирования, проектирования нейросетей, тестирования, управления внешними устройствами, вывода результатов и т.п. Главная ЭВМ сопрягается с аппаратурой SYNAPSE1 через шину VME.

В архитектуре SYNAPSE1 можно выделить четыре основные компоненты: матричный процессор, память весов, устройство управления и устройство данных со следующими характеристиками:

- процессорная плата с матрицей из 8 сигнальных процессоров МА 16 с производительностью 3,2 млрд. операций умножения (16?16 бит) и сложения (48 бит) в секунду;

- память весов 128 Мбит;

- устройство управления на базе MC68040;

- устройство данных на базе MC68040.

Все аппаратные средства размещаются в небольшом корпусе с габаритами 667?398?680 мм.

Проведённые исследования показали, что по производительности выполнение нейросетевых операций на нейрокомпьютере Synapse 1 по крайней мере на три порядка превышают производительность традиционных вычислительных систем и позволяют моделировать нейросети с количеством синапсов, равным 64 млн., а гибкость архитектуры практически не ограничивает разнообразие реализуемых нейросетевых парадигм.

Нейрокомпьютер 'Эмбрион'

Нейрокомпьютер 'Эмбрион' [6] (рис. 11) разработан под руководством член-корреспондента МАИ, В.Д. Цыганкова (sinteg@mail.ru).

На сегодня известно несколько модификаций данного нейрокомпьютера для различных приложений: датчик случайных многомерных управляемых импульсных потоков 'Эмбрион-1', интерсенсорный перенос 'глаз-рука', техническая диагностика неисправностей энергогенератора самолётной электростанции ('Эмбрион-2'), управление нестационарным объектом (ЛА) в реальном масштабе времени ('Эмбрион-3' и 'Эмбрион-4'), орган технического зрения ('Эмбрион-5'), управление тактильно-чувственным адаптивным промышленным роботом 'УНИВЕРСАЛ-5А' при обслуживании карусельной плавильной печи на стекольном заводе ('ПОИСК-1'), управление тактильно-чувственным адаптивным промышленным роботом 'Р-2' с искусственными мышцами при сборке и покраске ('ПОИСК-2'), управление тактильно-чувственным мобильным автономным роботом 'КРАБ-1' при взаимодействии с неориентированными предметами и др.

Виртуальный нейрокомпьютер 'Эмбрион' - модель мозга человека [6], возбуждение квазинейронов в нём создаёт виртуальное квантовое когерентное волновое поле, которое имеет прямое отношение к проблеме создания Квантового нейрокомпьютера (КНК). Нейрокомпьютер 'Эмбрион' представляет собой некоторую разновидность квантовой МАКРОсистемы или квантово-механической системы, то есть квантовый когерентный нейрокомпьютер, и требует для своего воплощения совершенно другой, по сравнению с обычным ПК, функциональной элементной базы или 'мозговой массы'.

Заключение

Работа с нейроускорителями и нейрокомпьютерами даёт в руки современного инженера-исследователя, аналитика мощное средство проведения вычислений в реальном масштабе времени. Если раньше большая часть времени уходила на подготовку и проверку одной-единственной гипотезы, то теперь система обрабатывает данные и выдаёт заключения практически в реальном времени. Несмотря на свои впечатляющие возможности, нейровычислители не очень распространены на рынке вследствие высокой цены (от единиц до десятков тысяч USD для нейроускорителей и от десятков до сотен тыс. USD для нейрокомпьютеров) и из-за специфики освоения. Основная причина отсутствия полнофункциональных нейровычислителей на рынке - закрытость разработок. Из сотен фирм, производящих специализированные нейрочипы, лишь единицы поставляют свою продукцию на массовый рынок. Остальные обслуживают военный комплекс либо создают единичные продукты для спецприложений.

К сожалению, из-за ограничений в объёмах в рамках одного обзора нет возможности рассказать подробно обо всех известных на сегодня нейровычислителях и нейрокомпьютерах, в дальнейшем мы постараемся периодически возвращаться к данной теме и обсуждать вопросы новых архитектурно-схемотехнических решений и элементной базы нейровычислителей. Оперативную информацию по данному направлению всегда можно получить на сервере 'Новости с Российского рынка нейрокомпьютеров' [3].

Материалы данного обзора являются основой курсов 'Микропроцессоры в системах управления' и 'Архитектура и схемотехника современных ЭВМ', читаемых на кафедре 'Конструирование и технология производства электронной аппаратуры' МГТУ им. Н.Э. Баумана (http://iu4.bmstu.ru).

Литература

1. Проблемы построения и обучения нейронных сетей / под ред. А.И. Галушкина и В.А. Шахнова. - М.: Изд-во Машиностроение. Библиотечка журнала Информационные технологии. - 1999. - ? 1. - 105 с.

2. Галушкин А.И. Некоторые исторические аспекты развития элементной базы вычислительных систем с массовым параллелизмом (80- и 90-е годы) // Нейрокомпьютер. - 2000. - ? 1. - С. 68-82.

3. http://neurnews.iu4.bmstu.ru.

6. Цыганков В.Д. Нейрокомпьютер и его применение. - М.: Сол Систем. - 1993.

Нейрокомпьютеры - архитектура и реализация. Часть 3.2. Аппаратная реализация нейровычислителей.

Нейрокомпьютеры - архитектура и реализация. Часть 3.2. Аппаратная реализация нейровычислителей.