|

Ю. Гончаров Технология разработки eXpressDSPВысокотехнологичные устройства на базе сигнальных процессоров захватывают вс╦ более широкие области применения. Темпы роста рынка постоянно ускоряются, что приводит к сокращению жизненного цикла изделия и требует сокращения временных и финансовых затрат на его разработку. С другой стороны, расширение областей применения и функциональных возможностей устройств приводит к их усложнению, что увеличивает время и стоимость цикла разработки. Рассмотрим основные факторы, удорожающие и удлиняющие цикл разработки. Отметим интересную особенность - при усложнении самих устройств ид╦т процесс упрощения разработки их аппаратной части за сч╦т применения интегральных программируемых компонентов. При этом основные затраты при разработке нового изделия приходятся на разработку программного обеспечения. По данным журнала "Embedded System Programming", на разработку программного обеспечения встроенных систем в настоящее время тратиться до 80% времени цикла разработки. Ещ╦ одним отрицательным моментом при традиционном подходе к разработкам является написание каждой программы как уникальной разработки с чистого листа, то есть очень редко используется уже разработанный код. Следующей проблемой, вытекающей из усложнения устройств, является усложнение средств тестирования и необходимого для работы измерительного оборудования. Стоимость необходимых приборов может съесть львиную часть бюджета разработки и даже при вложении существенных средств может возникнуть ситуация, когда разработчики будут вынуждены простаивать, ожидая своей очереди воспользоваться дорогостоящим прибором. Также нельзя забывать и о времени ожидания изготовления аппаратной части устройства, удлиняющем цикл разработки. Особенно это актуально в наших условиях, когда время на разработку и изготовление печатных плат с приемлемой стоимостью, особенно для сложных устройств, может составлять 2√3 месяца. С другой стороны, ускорение развития рынка предъявляет требования к ускорению и удешевлению цикла разработки изделия. Налицо явное противоречие между требованиями рынка и методами разработки. Разрешение возникающих противоречий и устранение мешающих факторов возможно только при качественном изменении самого подхода к проектированию ЦОС-устройств. Для решения этой проблемы фирмой Texas Instruments предложен новый подход к проектированию устройств на базе сигнальных процессоров - технология eXpressDSP. Это законченная целостная технология, включающая набор интегрированных программных и аппаратных средств и решений, а также методов разработки, что позволяет существенно ускорить и облегчить процесс разработки. Технология призвана обеспечить максимальный комфорт разработчику, максимально избавить его от рутинных операций и предоставить мощные средства разработки и отладки. В то же время, применение технологии eXpressDSP позволяет оперировать при разработке терминами операционных систем реального времени. Особенное место отводится средствам анализа и тестирования разработанной программы, что позволяет существенно сократить и облегчить этот этап. Основные составляющие технологии eXpressDSP и их назначениеПервым аппаратным элементом eXpressDSP является интерфейс внутрисхемной эмуляции на базе тестового интерфейса IEEE 1149 JTAG. Это стандартный тестовый интерфейс, применяемый для тестирования электронных компонентов и устройств. Он имеется в каждом ЦСП Texas Instruments и с рядом дополнений используется как интерфейс внутрисхемного эмулятора. Его использование позволяет легко и просто интегрировать средства внутрисхемной эмуляции в состав разрабатываемого устройства. Интерфейс JTAG да╦т возможность подключения одного или нескольких ЦСП к одному отладчику с использованием всего 6 сигнальных линий. Можно подключать к одному внутрисхемному JTAG-эмулятору несколько разнородных ЦСП и контроллеров. При этом обеспечивается гибкость подключения и высокая скорость обмена. Подключение отладочного JTAG-интерфейса и работу с ним обеспечивают внутрисхемные JTAG-эмуляторы. Отметим, что интерфейс JTAG является единым отладочным интерфейсом для всех ЦСП TI. Соответственно, внутрисхемный JTAG-эмулятор является единым аппаратным отладочным средством. При этом программное обеспечение является отдельным для каждого из семейств ЦСП. Следующим элементом является технология RTDX - технология обмена данными в реальном времени (Real Time Data Exchange). Она позволяет максимально использовать возможности JTAG-интерфейса, интегрируя в него помимо возможностей внутрисхемной эмуляции возможности обмена данными в реальном времени между ЦСП и хост-компьютером, на котором запускается отладочная среда. Использование технологии RTDX позволяет объединить отлаживаемый ЦСП и хост-компьютер в единую систему с мощными функциями тестирования и анализа в реальном времени. В качестве программного отладочного средства, работающего с внутрисхемными JTAG-эмуляторами и поддерживающего технологию RTDX, используется интегрированная среда разработчика (IDE) Code Composer Studio (CCS). Это интегрированный функционально законченный продукт, включающий в себя вс╦ необходимое для редактирования, компиляции, отладки и анализа программ. CCS имеет удобный реконфигурируемый пользовательский интерфейс с удобными средствами редактирования кода и развитой системой контекстной помощи, в которую автоматически включается система команд отлаживаемого ЦСП. Для удобства ведения сложных разработок в CCS входят графические средства конфигурированя и ведения проектов. Для компиляции программ в CCS используются оптимизирующие компиляторы ассемблера и Си. Использование языка высокого уровня Си и оптимизирующих компиляторов при написании ЦОС-приложений позволяет сочетать гибкость и скорость написания программы на языке высокого уровня и оптимальность написания ассемблерных кодов. Отметим, что для новых ЦСП TI свободно доступны оптимизированные на ассемблере библиотеки основных ЦОС функций с заголовками для вызова из Си-программ. B cостав CCS входит мощный многооконный отладчик, который имеет ряд особенностей, ориентированных именно на системы ЦОС. Отладочные средства CCS позволяют работать одновременно с несколькими ЦСП как по отдельности, так и интегрируя их в единую систему. Отладчик CCS имеет гибкую систему задания точек останова, вплоть до задания выражения на Си-подобном языке. Уникальной особенностью CCS является наличие точек подключения (Probe Points). Фактически это подключаемый к программе канал ввода/вывода. Точка подключения может быть использована для подачи и снятия сигналов, что совместимо со средствами файлового ввода/вывода и визуализации данных. Использование точек подключения да╦т пользователям CCS мощный инструмент анализа и тестирования программы. Добавление к этому средств анализа реального времени, базирующихся на технологии RTDX, превращает CCS в средство анализа и тестирования в реальном времени. CCS имеет открытую конфигурируемую архитектуру. В систему интегрирован внутренний Си-подобный язык сценариев GEL, который да╦т практически любые возможности настройки, вплоть до конфигурирования системы меню. Фактически можно программным пут╦м задать алгоритм поведения системы. Отметим, что язык GEL имеет развитую библиотеку функций, графических функций, а также широкую область действия, вплоть до задания условий выполнения точек останова и изменения содержимого памяти ЦСП. Совместное использование функций анализа и визуализации данных и языка GEL делает возможным построение на базе CCS мощного испытательного стенда для разрабатываемого устройства. Следующий элемент eXpressDSP - масштабируемое ядро реального времени DSP BIOS, включающее в себя средства обеспечения мультизадачности, работы с аппаратным обеспечением, средства реального времени и конфигурации. Это ядро разработано для приложений, работающих с запуском и управлением процессами в реальном времени, передачей данных между ЦСП и отладчиком. Средства DSP/BIOS могут использоваться как для мониторинга программ в реальном времени, так и в самих программах для обеспечения мультизадачности и обработки в реальном времени. DSP/BIOS можно разделить на 10 модулей, соответствующих четыр╦м основным группам функций:

При использовании средств DSP BIOS мы фактически переходим от написания программы с чистого листа к оперированию терминами многозадачной операционной системы реального времени. При этом отладочные средства предоставляют возможность контроля и управления поведением такой системы. Одним из ключевых компонентов технологии eXpressDSP является DSP Algorithm Standard - набор правил и при╦мов написания программных модулей. Использование DSP Algorithm Standard позволяет перейти к модульному структурированному подходу к написанию программ. Такой подход имеет целый ряд преимуществ. Программа уже не пишется как уникальный и нигде потом не используемый код. Она разбивается на модули, каждый из которых может быть написан отдельным разработчиком, что немаловажно в больших проектах, и затем все эти модули без проблем стыкуются между собой. Каждый из написанных модулей может быть затем отдельно пересмотрен, измен╦н или улучшен заново. Возможность сборки программы из отдельных написанных и оттестированных модулей породило рынок готовых реализаций алгоритмов, написанных в соответствии с DSP Algorithm Standard. Существует и развивается сообщество так называемых третьих поставщиков - фирм, выпускающих на рынок сертифицированные TI программные продукты, такие как, например, кодер MPEG или модем V.34. В данный момент зарегистрировано более 300 третьих поставщиков, и их количество постоянно увеличивается. При этом разные фирмы предлагают свои варианты реализации и конкурируют за покупателя, который волен выбрать наиболее подходящее ему решение и интегрировать его в свою систему. Практически любая фирма может выпустить свой модуль, зарегистрироваться в TI как третий поставщик, пройти сертификацию TI своего продукта и выйти с ним на рынок. Следующим моментом стандартизации является стандартизация интерфейсов приложений (API) для стандартной периферии, такой как АЦП и ЦАП. Фактически все новые аналоговые интерфейсы для ЦСП от TI снабжаются драйверами под технологию eXpressDSP. В состав драйвера входят функции инициализации устройства и обмена с ним потоками данных. Драйверами могут снабжаться не только аналоговые интерфейсы, но и прочая периферия, что в свою очередь созда╦т рынок третьих поставщиков аппаратных решений. Кроме драйверов для периферийных устройств, TI выпускает для ЦСП так называемые библиотеки поддержки чипа (Chip Support Library), в которые входят API для инициализации и управления составными частями ядра ЦСП и его периферийными устройствами, такими как контроллер ПДП, таймер или последовательный порт. Резюмируя, можно сказать, что разработчику ЦОС-систем предоставляется:

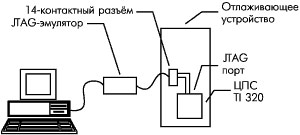

То есть фактически вс╦ обрамление, кроме собственно разрабатываемого алгоритма. При этом все элементы оттестированы и состыкованы и оста╦тся только написать сам алгоритм. Прич╦м для написания программных модулей тоже существует стандарт, позволяющий без проблем стыковать их друг с другом и с окружением. Мало того, существует рынок уже написанных модулей, которые можно интегрировать в разрабатываемое решение. Можно сказать, что использование технологии eXpressDSP переводит разработку программного обеспечения на новый уровень. Во-первых, разработчику да╦тся инструмент, позволяющий оперировать в терминах многопотоковых систем реального времени. При этом большую часть рутинной работы по отработке стандартных операций и достаточно тонкие и сложные вопросы обеспечения распределения времени берут на себя стандартные средства. Во-вторых, разработчик получает мощный измерительный и испытательный комплекс с широкими функциональными возможностями, заменяющий целый ряд дорогой измерительной аппаратуры. В технологию eXpressDSP как составная часть входит и широкий набор модулей-прототипов с продуманной архитектурой и широкими функциональными возможностями. Их использование совместно с остальными элементами технологии eXpressDSP позволяет оценить разрабатываемую систему и отработать применяемые решения на "живом" устройстве на самых ранних стадиях разработки. Не следует забывать и об оказываемой TI широкой информационной поддержке разработчиков. В не╦ входит полная и свободно доступная документация на все микросхемы, материалы по применению ЦСП, материалы по их итеграции с другими компонентами. Также свободно доступны примеры как готовых алгоритмов, так и реализации основных ЦОС функций. Все эти информационные материалы помогут правильно сориентироваться и оценить предстоящую разработку и существенно облегчат работу за сч╦т использования готовых стандартных решений. Внутрисхемные JTAG-эмуляторыВсе ЦСП фирмы TI имеют единый отладочный интерфейс JTAG и работают с внутрисхемным JTAG-эмулятором. Отлаживаемый процессор и эмулятор соединяются по интерфейсу JTAG через специальные выделенные на процессоре выводы. Такое подключение да╦т возможность отлаживать устройство в той конфигурации и на том процессоре, с которым оно будет работать. Это снимает как вопросы быстродействия эмулятора, так и вопросы изменения электрических параметров при подключении эмулятора. Подключение внутрисхемного эмулятора полностью прозрачно для исполняемой программы и не оказывает на е╦ выполнение никакого влияния. При этом программа исполняется на полной скорости процессора без каких-либо задержек и ограничений по производительности. Внутрисхемные JTAG-эмуляторы выпускаются как самой фирмой Texas Instruments, так и несколькими сертифицированными третьими поставщиками, в том числе и отечественными. Внутрисхемный JTAG-эмулятор SDSP-510

На Российском рынке хорошо зарекомендовал себя выпускаемый Воронежским инженерным центром компанией SCAN - фирмой SET - внутрисхемный эмулятор SDSP-510, являющийся полным функциональным аналогом оригинального устройства TI - эмулятора XDS-510, но при этом имеет в несколько раз меньшую стоимость. Ещ╦ одним преимуществом JTAG-эмулятора является возможность его подключения к уже готовому устройству, из которого выведен JTAG-разъ╦м. Для мобильных применений, для подключению к носимым компьютерам, а также для работы с компьютерами, которые не имеют шины ISA, выпускается внутрисхемный JTAG-эмулятор для подключения к параллельному порту SDSP-PP. Внутрисхемный JTAG-эмулятор SDSP-510

Несмотря на использование в качестве интерфейса параллельного порта, скорость работы через SDSP-PP практически не изменяется за сч╦т того, что используются высокоскоростные двунаправленные режимы обмена. Использование внутрисхемного JTAG-эмулятора радикально отличается от традиционного подхода, при котором предполагается подключение на место процессора либо специальной микросхемы-прототипа, либо специального устройства - эмулятора. Это снимает массу возникающих при использовании традиционной технологии проблем:

При использовании технологии JTAG мы переходим от эмуляции процессора внешним устройством к непосредственному контролю над процессором при выполнении программы. Это снимает ещ╦ несколько проблем. Во-первых, эмулятор всегда будет работать на полной скорости процессора без каких-либо ограничений. Во-вторых, аппаратное обеспечение внутрисхемного эмулятора для всех версий данного ЦСП, да и для всех ЦСП фирмы TI, одинаково - различия учитываются на уровне программного обеспечения, что снимает проблему поддержки эмулятором вновь выпускаемых версий процессора. То есть как бы ни модернизировалось ядро процессора, какую бы периферию ни добавляли на кристалл, можно всегда быть уверенным, что эмулятор будет поддерживать все эти модификации. Изменения может потребовать только программное средство, которое с ним работает - Code Composer. При переходе на другое семейство ЦСП аппаратное обеспечение оста╦тся тем же. Достаточно только установить соответствующую версию Code Composer, и можно работать. Такой подход обеспечивает уникальную гибкость при выборе базы для разработки устройства и позволяет выбрать наиболее подходящий процессор или поменять его в процессе разработки. Снимается вероятность возникновения очень неприятной ситуации, когда надо делать устройство именно на этом ЦСП потому, что его поддерживает имеющийся эмулятор, а для перехода на другой ЦСП надо покупать ещ╦ один эмулятор, что очень дорого. Особо отметим, что тестовый интерфейс JTAG имеется в каждом серийно выпускаемом процессоре, и поэтому просто установив ЦСП от TI в разрабатываемое устройство и подключив к нему внутрисхемный JTAG-эмулятор, мы сразу без дополнительных аппаратных затрат получаем все возможности технологии eXpressDSP по анализу и отладке программного обеспечения, а также широкие возможности тестирования устройств при его серийном выпуске. Рассмотрим подробнее тестовый интерфейс JTAG и принципы работы внутрисхемных JTAG-эмуляторов. Тестовый интерфейс JTAGИнтерфейс JTAG назван по сокращ╦нному названию образованной в 1985 году группы ведущих производителей электронных компонентов (Joint Test Action Group), которая была создана для решения проблем тестирования сложных электронных устройств. Выработанная группой архитектура последовательного тестового интерфейса была принята как промышленный стандарт IEEE Std. 1149.1-1990 (IEEE Standard Test Access Port and Boundary-Scan Architecture). Данная архитектура называется ещ╦ по наименованию стандарта - Boundary-Scan Architecture - архитектура граничного сканирования. Интеграция архитектуры BSC в устройство

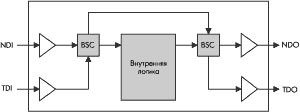

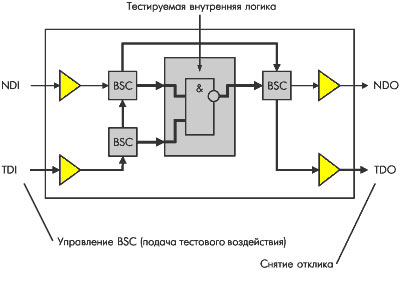

Встраивание архитектуры BST в устройство предполагает обеспечение доступа к выводам микросхемы, точнее, к специальным блокам ввода/вывода - BSC. При этом предусматривается возможность как контроля состояния вывода при помощи BSC, так и управление состоянием вывода. BSC располагаются между блоками ввода/вывода и внутренней логикой микросхемы и последовательно включаются в последовательную тестовую цепочку - отсюда и называние - архитектура последовательного сканирования. Точнее сказать, что BSC встраиваются в блоки ввода/вывода. В обычном состоянии BSC не оказывают никакого влияния на работу устройства, и сигналы свободно проходят со входа NDI и внутренней логики устройства на выход NDO. В режиме тестирования последовательно включенные BSC позволяют задавать на своих выходах тестовые воздействия при помощи подаваемых на вход TDI сигналов и снимать со входов BSC отклик, выводимый по линии TDO. Использование JTAG для тестирования межсоединений

Такое подключение позволяет контролировать и межсоединения микросхем (рис. 4) и внутреннюю логику работы (рис. 5) без использования пробников с физическим контактом. Использование JTAG для тестирования внутренней логики

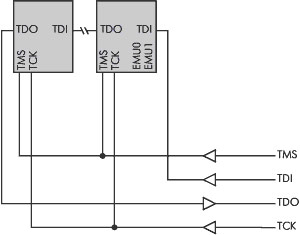

Каждое совместимое со стандартом IEEE Std. 1149.1 устройство имеет 4 дополнительных вывода: вход управления TMS, тактовый вход TCK, последовательный вход данных TDI и последовательный выход данных TDO. Внутри устройства предусматривается специальный контроллер, состоящий из блока управления, называемого портом тестового доступа TAP (Test Access Port) и целого набора сдвиговых регистров: регистра команд, тестового регистра, регистра пропуска и возможных пользовательских регистров. ТАР управляет переключением потока данных между регистрами. Его состояние определяется последовательностью взаимных состояний тактового сигнала TCK и сигнала управления TMS. В зависимости от состояния TAP, в состав JTAG-пути всегда включается один из регистров. Регистр команд служит для при╦ма поступающих команд. Они определяют состояние контроллера и устройства, а также интерпретацию блоками BSC поступающих с TDI данных. Существует набор обязательных команд стандарта IEEE 1149, которые должны поддерживаться всеми устройствами. Это команды инициализации, задания режимов работы, считывания статуса, считывания идентификатора устройства и другие. Кроме того, для каждого устройства могут быть определены свои специфичные расширения системы команд. Регистр пропуска (BYPASS) - однобитовый регистр, позволяющий уменьшить длину JTAG-пути. Ещ╦ одной функцией регистра пропуска является возможность прозрачной ретрансляции данных через JTAG-контроллер. Последовательно включенные блоки BSC образуют тестовый регистр. Соединение нескольких устройств интерфейсом JTAG

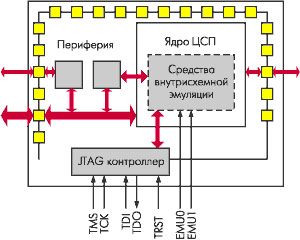

Пользовательские регистры специфичны для каждого устройства и выполняют дополнительные функции, например, доступ к тестовым блокам процессора или управление конфигурацией ПЛИС. Все устройства последовательно соединяются входами и выходами данных, при этом все сдвиговые регистры соединяются в цепочку, образуя JTAG-путь (JTAG scan path). При этом любое устройство неявно адресуется своим положением в цепочке. Проверку того, что операция производится именно с требуемым устройством, можно провести, считав его 32-бит идентификатор, который включает в себя идентификатор производителя, идентификатор устройства и его версию. Производители микросхем предоставляют информацию о реализации JTAG-контроллера и соответствии тестового регистра внешним выводам устройства в специальных файлах в стандартизованных форматах, например BSDL. Подробное описание форматов можно найти на http://www.ti.com/sc/docs/jtag/format.htm. Отметим также ещ╦ одну важную особенность стандарта JTAG. Поскольку в одну цепочку могут подключаться разные устройства разных производителей со своими специфичными особенностями, то функции делятся на две части: общие, обязательные для поддержки всеми устройствами, и специфичные для данного устройства. Это позволяет программному и аппаратному обеспечению, предназначенному для работы с одним устройством, получать доступ к нему без наличия полной информации об остальных устройствах JTAG-цепочки и их особенностях. Использование JTAG как отладочного интерфейса в ЦСП Texas InstrumentsВсе выпускаемые на данный момент ЦСП Texas Instruments имеют тестовый интерфейс JTAG, который, как и полагается по стандарту, охватывает все блоки ввода/вывода внешних выводов процессора и может использоваться для тестирования межсоединений устройства. Файлы BSDL описания этого JTAG-интерфейса свободно доступны с ftp-сервера Texas Instruments. Кроме этого, сигнальные процессоры имеют ещ╦ и дополнительные JTAG-пути и регистры, ведущие в ядро ЦСП и к его периферийным модулям. Эти пути используются отладочными средствами Texas Instruments для выполнения функций внутрисхемной эмуляции. То есть в ЦСП TI интерфейс JTAG используется как для тестирования межсоединений на плате, так и для доступа к внутренним ресурсам процессора. ЦСП может включаться в JTAG-путь совместно с другими установленными на плате устройствами, которые при работе внутрисхемного эмулятора просто ставятся в режим BYPASS. Интеграция средств JTAG в ЦСП Texas Instruments

ЦСП Texas Instruments имеют ряд дополнительных выводов: вход сброса JTAG-интерфейса - TRST и два входа эмуляции - EMU0 и EMU1. Все линии выводятся на стандартный 14-контактный разъ╦м. Интерфейс JTAG допускает последовательное соединение нескольких устройств, в данном случае, нескольких ЦСП, а также других JTAG-устройств. Однако при этом следует учитывать, что средства работы с JTAG-архитектурой, предназначенные для тестирования, как правило, работают на малой скорости, а средства внутрисхемной эмуляции для ЦСП Texas Instruments используют практически максимальную для стандарта частоту обмена - около 10 МГц. Подключение внутрисхемного JTAG- эмулятора к отлаживаемому устройству

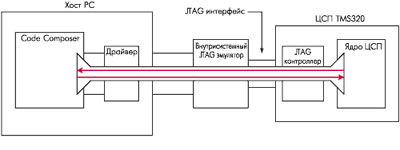

К порту JTAG подключается специальное устройство, называемое внутрисхемным JTAG-эмулятором. С другой стороны JTAG-эмулятор подключается к компьютеру. В настоящее время существуют JTAG-эмуляторы для подключения к шине ISA и для подключения к параллельному порту компьютера. Основное назначение внутрисхемного JTAG-эмулятора - обеспечить интерфейс между JTAG-портом ЦСП и компьютером. Совместно с JTAG-контроллером, внутрисхемный эмулятор обеспечивает канал связи между расположенными в ЦСП отладочными узлами и запущенной на PC отладочной средой. Обеспечение средствами JTAG канала между ЦСП и отладчиком

Подключенное к JTAG-порту отладочное средство может не только контролировать и управлять ядром ЦСП, но для него доступны также все доступные для ядра периферийные блоки и банки памяти, прич╦м независимо от того, размещены они на кристалле или вне его. Например, при доступе к внешнему ОЗУ средствами внутрисхемной эмуляции выда╦тся команда на блок управления внешней шиной, и он генерирует цикл обращения к внешнему ОЗУ. Отметим, что доступ к периферийным устройствам при обращении к ним из отладчика производится теми же средствами, что и при доступе к ним исполняемой на ЦСП программы. При этом такая операция "прозрачна" для состояния ядра ЦСП и для программы, а с точки зрения периферийного устройства по алгоритму обмена и его временным параметрам, полностью аналогична обращению при выполнении программы, ведь это обращение выполняется одним и тем же блоком, только команды на него поступают от встроенных средств тестирования через тестовый JTAG-интерфейс. Такой подход позволяет средствам отладки работать не только со стандартными узлами ЦСП, но также и с разработанными пользователем и подключенными к внешним шинам чипа периферийными устройствами. Само подключение внутрисхемного эмулятора абсолютно прозрачно для исполняемой программы и не оказывает на е╦ исполнение никакого влияния. При этом программа исполняется на полной скорости процессора без каких-либо задержек и ограничений по производительности. Поскольку стандарт JTAG поддерживает подключение нескольких устройств, то и к внутрисхемному JTAG-эмулятору можно подключить несколько ЦСП и работать с ними как одновременно, так и поодиночке. Итак, мы имеем процессор и подключенный к нему внутрисхемный эмулятор. В следующей статье цикла мы перейд╦м к рассмотрению интегрированной отладочной среды Code Composer Studio, которая работает с этими аппаратными средствами. |

|

|

|

|

PDFs | Новости | Литература | Схемы | Форум | Блоги | Реклама |

Технология разработки eXpressDSP.

Технология разработки eXpressDSP.