|

Генри Верхейен (перевод Ю. Потапова) Проблемы целостности сигналовС наступлением эры субмикронных и нанометровых технологий (0,18 микрон и ниже) интегральные схемы стали работать на высоких частотах и потреблять больший ток и мощность при меньших напряжениях питания. Это привело к более яркому проявлению эффекта паразитной емкостной связи. Кроме того, масса других паразитных эффектов, которые можно было не учитывать в проектах предыдущего поколения, стали ключевыми факторами для обеспечения правильного функционирования и высокой производительности новых микросхем повышенной плотности. В современных условиях проблема взаимосвязи таких параметров, как скорость, потребляемая мощность, целостность сигналов и над╦жность, стала столь же актуальной, как и проблема снижения площади кристалла для устройств предыдущего поколения. Что такое целостность сигналов?Хотя на настоящий момент не существует универсального общепринятого определения такого понятия, как целостность сигналов, оно охватывает все физические эффекты, проявляющиеся при проектировании интегральных схем и приводящие к их неправильному функционированию или искажению формы сигналов. Наиболее заметным из них является эффект паразитной емкостной связи между проводниками, приводящий к возникновению в них перекр╦стных искажений. Кроме него, на целостность сигналов влияют:

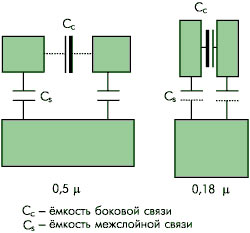

Перекр╦стные искажения возникают из-за взаимной емкостной связи между проводниками микросхемы, в результате чего при изменении уровня сигнала в проводнике форма сигнала в соседних проводниках также изменяется. Эти эффекты почти не проявлялись при использовании технологии с шириной проводников 0,5 мкм и больше. По мере повышения плотности схем и перехода к 0,25-мкм и меньше технологии, емкостная связь начинает расти вследствие сближения проводников и роста их относительной толщины. Рис. 1 показывает, что ╦мкость связи Cc в устройстве, выполненном по 0,18-мкм технологии выше, чем в 0,5-мкм.

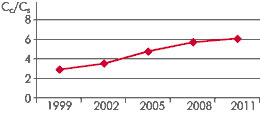

Мерой оценки эффекта перекр╦стных искажений является отношение ╦мкости боковой связи Cc, возникающей между проводниками, расположенными на одном слое, к ╦мкости межслойной связи Cs, возникающей между проводниками, расположенными на разных слоях. Эффект взаимосвязи становится более видным, поскольку развитие технологии приводит к использованию геометрических объектов меньшего размера. Согласно докладам, представляемым на регулярно проходящей международной конференции International Technology Roadmap for Semiconductors, ╦мкость боковых связей для технологий 1999 года превышала ╦мкость межслойных связей почти в три раза, а к 2006 году это соотношение достигнет пяти (рис. 2).

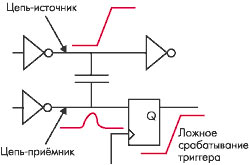

Наиболее ярко перекр╦стные искажения проявляются в проводнике-при╦мнике при изменении уровня сигнала в проводнике-источнике. При анализе этого эффекта подразумевается выбор одной из цепей в качестве при╦мника помехи, а всех остальных окружающих е╦ цепей в качестве источников. Когда цепь-при╦мник находится в покое (собственный сигнал в ней отсутствует) или в установившемся состоянии (собственный сигнал присутствует, но его уровень не изменяется) анализ перекр╦стных искажений может быть провед╦н в статическом режиме. Если в результате скачков напряжения на проводниках-источниках в цепи-при╦мнике наводится сигнал уровня, достаточного для того, чтобы изменить е╦ логическое состояние (из логической "1" в "0" или наоборот), это может вызвать срабатывание последующих устройств, например, триггера (рис. 3), что в свою очередь приводит к неправильному функционированию системы.

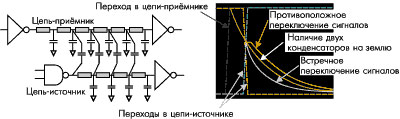

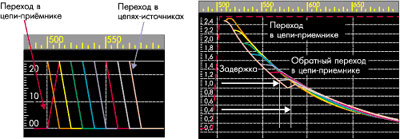

Часто явление перекр╦стных искажений приводит к неустойчивой синхронизации сигналов, особенно когда периоды переключения (фронты) в цепи-при╦мнике и цепи-источнике перекрываются. Когда переключение сигналов в цепях происходит в противоположных направлениях, это может стать причиной запаздывания сигнала в цепи-при╦мнике или увеличения его длительности. При сонаправленном переключении сигналов длительность импульса в цепи-при╦мнике может оказаться короче, что привед╦т к сокращению времени удержания в триггерах и защ╦лках. Задержка фронта, возникающая в результате перекрытия периодов переключения в цепях, не может быть смоделирована точно посредством замены ╦мкости связи на эквивалентную схему с емкостями, соедин╦нными с земл╦й, как показано на рис. 4 (2 конденсатора ≈ на землю в случае встречного изменения сигнала и ни одного конденсатора при сонаправленном изменении сигналов). Здесь начинает работать отношение ╦мкости связи к суммарной ╦мкости цепи, являющееся важной переменной при анализе эффектов перекр╦стных искажений. Это отношение предоставляет ценную информацию и может быть использовано при отбраковке изделий. Однако, оно не обладает количественной информацией, необходимой для оценки эффектов перекр╦стных искажений. Для корректного моделирования этих эффектов необходим такой инструмент анализа, который может моделировать динамическую скорость переключения. Для правильной оценки перекр╦стных искажений нужна также информация о времени переключения в цепи источника. На рис. 5 показано, что, в зависимости от времени переключения в цепях-источниках, временная задержка в цепи-при╦мнике может быть различной.

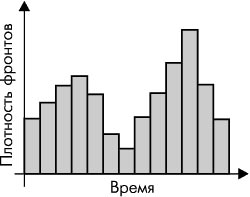

Современные методы анализа перекр╦стных искажений применяются после разработки топологии, когда программа моделирования схемотехнического уровня (например, Spice), использующая специальные модели и векторы, пытается проанализировать все паразитные эффекты на подложке и идентифицировать проблему. Обнаруженные проблемы, как правило, решаются корректировкой топологии. Самые современные системы используют или специальные дополнительные методы моделирования, позволяющие анализировать временные эффекты в статическом режиме на транзисторном и вентильном уровнях, или специальные программы моделирования, способные решать задачи по расч╦ту и идентификации помех. Однако, в целом процедура анализа перекр╦стных искажений, возникающих из-за паразитных емкостных связей, достаточно утомительна, и решение любой идентифицированной проблемы требует больших усилий. Рекомендации по ручному исправлению работают лишь для узкого круга практических задач. В общем случае, такой подход требует нескольких последовательных итераций постановки задачи и моделирования, что может привести к значительному увеличению времени проектирования. Поскольку указанные проблемы желательно идентифицировать до топологического проектирования, существуют другие системы, производящие анализ перекр╦стных искажений уже во время размещения и трассировки схемы. Существует набор эвристических правил, которые служат критериями первичной идентификации проблем перекр╦стных искажений (например, максимально допустимое значение длины двух параллельных проводников) на этапе трассировки проекта, после чего автоматически запускается программа моделирования, производящая более подробный анализ данного участка топологии. Как только критическое место будет выявлено, автотрассировщик попробует изменить топологию таким образом, чтобы или увеличить расстояние между данными цепями, или разместить их в разных слоях. Для большинства сложных и высокоскоростных проектов это может потребовать значительных усилий по разрыву и восстановлению проводников без гарантии полного решения проблемы в автоматическом режиме. Улучшенный подход к трассировке заключается в принудительном ограничении на длину любых двух параллельно проложенных проводников. Однако, он базируется на эмпирических данных и не отражает всю физику эффекта перекр╦стных искажений, где присутствует зависимость от взаимного расположения фронтов сигналов в разных цепях. Указанное ограничение может оказаться неоправданно ж╦стким, что привед╦т к перегрузке программы трассировки. Кроме того, здесь не может быть определена средняя длина цепей, максимально подверженная перекр╦стным искажениям, и проблема сохранится. Ряд компаний уже сообщили о существовании интеллектуальных систем автотрассировки, правильно понимающих эффекты перекр╦стных искажений, но они ещ╦ несовершенны и могут привести к перегрузке трассировщика из-за чрезмерно ж╦стких ограничений. Далее, в случае отсутствия точной информации о времени прихода сигналов, оценка перекр╦стных искажений может быть выполнена с большим запасом, что так же пагубно отразится на результатах трассировки. Новый подход к анализу перекр╦стных искаженийИдентификация проблем перекр╦стных искажений на этапах трассировки или обработки уже готовой топологии является слишком запоздалой, использование же системы анализа на посттопологическом этапе и вовсе неприемлемо из-за значительного увеличения времени проектирования. Новый подход ориентируется на раннее выявление перекр╦стных искажений и их подавление во время размещения или глобальной трассировки, что достигается непрерывной обработкой моделей. Здесь физическое проектирование прогрессивно разделено на небольшие ячейки с оптимизацией связности, синхронизации, мощности и перегрузки на всех этапах, включая анализ перекр╦стных искажений. Основой для решения проблем перекр╦стных искажений является интегрированный, инкрементный статический анализатор временных характеристик, учитывающий паразитные физические процессы и имеющий механизм экстракции RC-схем замещения связанных цепей. В самых современных инструментах такой анализатор временных характеристик позволяет смоделировать перекрытие фронтов сигналов в различных цепях и выявить потенциально опасные места схем. Так как на данном этапе в проекте ещ╦ не имеется никакой информации о топологии устройства, для выявления проблемных мест может быть использован статистический метод. Анализ фронтов сигналов в схеме позволяет построить гистограммы, на которых изображается зависимость плотности распределения фронтов от времени с уч╦том времени переключения сигнала в цепи-при╦мнике (рис. 6).

Сложность моделей связей снижается с понижением е╦ уровня. Основные исследования по анализу перекр╦стных искажений на базе информации о фронтах сигналов проводились в университете Carnegie Mellon. Согласно разработанной здесь технологии, цепи с сигналами, которые являются потенциальными жертвами перекр╦стных искажений, будут иметь дополнительные признаки, предписывающие системе глобальной трассировки выполнить для этих цепей или большие зазоры, или экранирование, или повторную разводку в системе локальной трассировки. Локальный трассировщик представляет собой бессеточную (основанную на точных геометрических формах) систему автоматической трассировки, позволяющую изменять ширины проводников и зазоры между ними с целью подавления перекр╦стных искажений. Он включает механизмы, позволяющие напрямую связать ограничения, направленные на снижение перекр╦стных искажений, с весовыми оценками качества трассировки и избежать влияния искажений на длительность фронтов и задержки в цепях. Аналогичным образом производится анализ шумов, возникающих в результате наличия паразитных связей. Здесь вместо анализа вклада перекр╦стных искажений в задержке тракта производится моделирование формы навед╦нного сигнала в цепи-при╦мнике. Если навед╦нный сигнал превышает порог, заранее заданный для логической ячейки, управляемой данной цепью, то нарушение будет выявлено и устранено локальным трассировщиком. ЭлектромиграцияСубмикронные технологи принесли в электронику проблемы электромиграции и дезинтеграции цепей в кристаллах вследствие наличия высокой плотности тока. По мере усложнения и увеличения скорости схем, через соединения будут протекать большие токи. В то же время, по мере совершенствования технологии фотолитографии, проводники становятся уже, достигая ширины 0,13 микрон. Плотность тока, определяющая его количество, протекающее через проводник единичной площади сечения, раст╦т нелинейно по мере снижения топологических проектных норм. Производство уже не может обеспечивать площадь сечения проводников, необходимую для гарантии целостности цепи в диапазоне используемых ширин. Когда слишком высокая плотность тока воздействует на проводники в течение длительного времени, металл разрушается, что приводит к появлению обрывов и коротких замыканий и, как следствие, к отказу всего устройства. В результате, это может закончиться забракованием всей партии дорогостоящих микросхем. На рис. 7 приведена фотография проводника, поврежд╦нного в результате проявления электромиграции.

Электромиграция традиционно рассматривалась как проблема устройств с широкими шинами питания и решалась на окончательных этапах разработки проекта. Однако, в современных условиях это неприемлемо, так как теперь перегрузка может произойти и в сигнальных цепях. Исследование эффектов электромиграции стало важным и для цепей синхронизации, где число контактов и межслойных соединений может быть недостаточным для протекания требуемого тока. Решение, которое обеспечит достаточное значение ширины проводников без излишних запасов, появилось совсем недавно и теперь предлагается рядом компаний √ производителей систем САПР. Подход состоит в том, чтобы идентифицировать потенциальные проблемы, связанные с плотностью тока в данной топологии, и устранить их посредством е╦ изменения. Однако этот посттопологический этап подразумевает тщательную экспертизу схемы и топологии, увеличивающую время цикла проектирования. Это далеко не единственный недостаток данного метода. Так, увеличение ширины проводника в современных проектах может быть просто невозможным, а это означает возвращение на этап разработки топологии, переработку е╦ уже с уч╦том результатов, полученных в предыдущем цикле проектирования, и дополнительные потери времени. Отсюда вывод: анализ эффектов электромиграции на посттопологическом этапе проектирования является слишком запоздалым. Наилучшим решением проблем электромиграции является определение правильной ширины проводников по мере их размещения. Именно такой подход используют современные системы САПР, рассчитывающие рекомендуемую ширину проводников в процессе их размещения. Ток, протекающий в каждом проводнике во время перехода уровня, рассчитывается специальным модулем моделирования. Результат такого расч╦та достаточно точный, так как здесь учитываются правильные емкостные нагрузки анализируемых цепей. Среднее или среднеквадратичное значение тока связывается с частотой переключения сигналов в цепях, полученной из результатов предыдущих этапов моделирования (например, из VCD-файла системы моделирования Verilog) или через сч╦тчики переходов, используемых во встроенной системе моделирования. По мере перехода проектов к более узким проводникам и сотням миллионов вентилей, возрастает важность связанных с электромиграцией тепловых эффектов, известных как эффекты саморазогрева, особенно в цепях сигналов и синхронизации. По информации о мощности, потребляемой логическими ячейками в пределах ограниченной площади кристалла, современные системы проектирования могут вычислить для не╦ среднюю температуру, используемую для получения рекомендуемой ширины проводников и числа межслойных соединений. После этого глобальная система трассировки может выделить требуемую площадь для работы локального трассировщика. Заметим, что описанный подход не требует посттопологического анализа эффектов электромиграции и ручного исправления выявленных проблем. Паразитное падение напряжения на внутреннем активном сопротивленииПроблема падения напряжения проявляется при протекании большого тока в резистивных цепях питания или заземления. В результате этого снижается быстродействие. По мере перехода к субмикронным технологиям, проблема паразитного падения напряжения становится ещ╦ более актуальной из-за следующих факторов:

Например, на сопротивлении 1 Ом при токе величиной 1 А падение напряжения составляет 1 В, что соответствует 2/3 от напряжения питания 1,5 В. В этом случае в микросхеме может произойти отказ по одной из следующих причин:

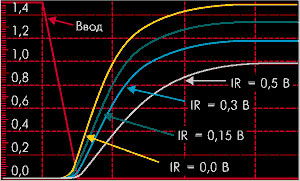

Рис. 8 демонстрирует влияние эффекта паразитного падения напряжения в цепи питания VDD на характеристики буферного элемента. Из-за снижения напряжения в цепи питания во фронтах импульсов появляются дополнительные задержки. В общем случае, эти проблемы могут быть выявлены только на этапе прототипирования, когда первые экземпляры устройств поступают с производства. Однако, усилия по идентификации проблемного элемента схемы могут привести к существенному увеличению длительности цикла производства. В большинстве проектов разработчики пытаются избежать возможного проявления описываемых эффектов пут╦м использования неоправданно широких шин питания и специальной топологии. Однако, соответствующее этому сокращение доступных для трассировки ресурсов в современных условиях недопустимо.

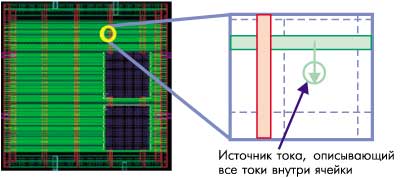

В последнее время различные компании, производители систем САПР, предлагают собственные инструменты для динамического анализа паразитных падений напряжения в цепях в моменты переключения. Как правило, для точной оценки падения напряжения необходима программа моделирования на транзисторном уровне. Во время размещения и трассировки схемы список е╦ соединений, необходимый для запуска программы моделирования, как правило, отсутствует, а сам запуск может занять много времени и привести к неоправданному замедлению процесса проектирования. Требование значительных вычислительных ресурсов накладывает ограничения на посттопологический анализ устройства и может стать причиной задержки передачи проекта в производство. Благодаря использованию моделей питания на уровне вентилей, можно будет отказаться от списка соединений. Однако, требуемые в этом случае вычислительные ресурсы ещ╦ слишком велики, чтобы допустить проведение анализа по мере практического размещения и трассировки схемы. Присутствует также проблема зависимости результатов, полученных на транзисторном и вентильных уровнях моделирования, а также реальных характеристик кристалла. Решение проблем паразитного падения напряжения кроется в раннем их обнаружении: на этапах размещения и глобальной трассировки. В этом случае нагрузки могут быть получены достаточно точно, и ещ╦ оста╦тся определ╦нная свобода для размещения ячеек, благодаря чему устраняются проблемы синхронизации и некоторые другие проблемы субмикронных технологий. Структура системы питания должна быть определена на этапе физического прототипирования, так как сильно влияет на трассировку сигнальных цепей, перегрузку трассировщика и размещение ячеек на последующих этапах. Для анализа паразитного падения напряжения все токи внутри ячеек суммируются и представляются в виде одного источника тока. Такие источники располагаются в некоторой сетке питания (рис. 9). Далее по результатам работы быстрого анализатора падений напряжения строится цветовая карта прогрева кристалла и производится корректировка сети питания для минимизации паразитных эффектов. Как правило, сеть питания строится со значительным запасом. Анализ позволяет получить оптимальные значения ширины проводников на различных участках сети питания и выиграть значительное количество места на кристалле. Если изначальная сеть питания не удовлетворяет рассчитанным значениям токов в ячейках, то ширина проводников будет увеличена, а возможно и будут добавлены дополнительные проводники. Пользователь может провести также анализ "что, если" и выявить дополнительные пути оптимизации проекта.

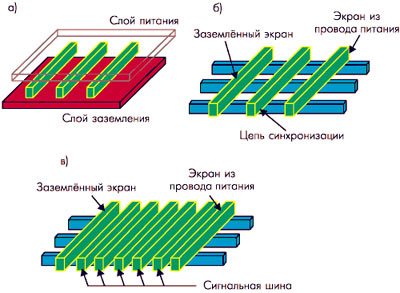

ИндуктивностьПо мере того, как с развитием 0,13-мкм технологии частота синхронизации превысила 500 МГц, в кристаллах стали проявляться индуктивные эффекты, способные причинить значительный вред специализированным (ASIC и ASSP) устройствам. Моделировать абсолютно все индуктивные связи и эффекты самоиндукции в устройстве нет никакой необходимости, так как индуктивный эффект является критическим только для цепей с высокочастотными сигналами, эффект самоиндукции "на кристалле" является важным только для длинных цепей, а эффект взаимоиндукции влияет только на длинные параллельные участки цепей. Чтобы снизить индуктивные эффекты, наиболее важно обеспечить правильный путь возвращения высокочастотных токов в общий провод. Эта задача чрезвычайно затруднена для автоматических инструментов размещения и трассировки, так как в настоящее время нет достаточно точного механизма анализа происходящих в них эффектов. Тем не менее, для схем, критичных к индуктивным эффектам, существуют специальные рекомендации по проектированию. Во-первых, устройство должно иметь сигнальные слои, расположенные между двумя сплошными слоями питания и заземления (рис. 10а), хотя она больше не используется из-за высокой стоимости производства и потребляемой мощности. Во-вторых, экранировать цепи синхросигналов надо так, чтобы высокочастотные токи возвращались в общий провод, расположенный на том же слое параллельно цепи синхронизации (рис. 10б). Третья рекомендация заключается в использовании общего провода, проложенного вдоль шины сигналов, из расч╦та один земляной провод на 4√8 сигнальных (рис. 10в).

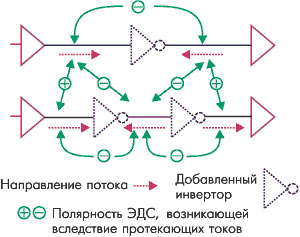

Как уже говорилось, индуктивные эффекты критичны для цепей с высокоскоростными или высокочастотными сигналами. Для длинных проводников, современные инструменты проектирования автоматически добавляют инверторы (рис. 11), чем достигается подавление этих эффектов. Лучший же способ заключается в том, чтобы осуществить такую глобальную и локальную стратегию трассировки, которая устраняет потребность в подробном моделировании и анализе индуктивных эффектов.

EEdesign Exclusive |

|

|

|

|

PDFs | Новости | Литература | Схемы | Форум | Блоги | Реклама |

Проблемы целостности сигналов.

Проблемы целостности сигналов.