|

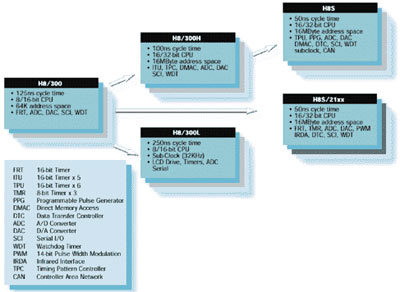

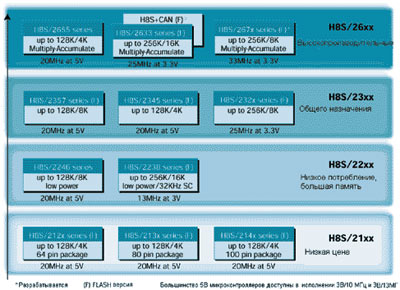

Д.Чоловсий 16-бит микроконтроллеры фирмы HITACHI серии H8S. Часть 1Микроконтроллеры HITACHI пользуются устойчивым спросом на европейском рынке. По итогам 1999 года компания Hitachi занимала там второе место по объ╦му продаж 16-бит микроконтроллеров, третье место по поставке 4-бит, шестое - по поставке 8-бит и второе место в мире по поставке 32-бит RISC-микроконтроллеров. В результате многолетней работы компании Hitachi и е╦ стремления удовлетворить требования заказчиков появились 16-разрядные микроконтроллеры серии H8/300H. H8S - ответ Hitachi на требования большей производительности и снижения энергопотребления при лучшем соотношении "цена/быстродействие". Микроконтроллеры стали снабжать памятью большего объ╦ма и усовершенствованной периферией, что позволило создать однокристальные системы там, где раньше требовалось несколько элементов. Включение такой структуры в однокристальную систему способно значительно снизить электромагнитные излучения, что чрезвычайно важно для современной электронной промышленности. Семейство микроконтроллеров H8S является частью программно совместимого ряда изделий Н8 (рис. 1). Hitachi предлагает микроконтроллеры Н8S в различных типах корпусов и с разными температурными режимами. H8S включает в себя более 25 вариантов высокопроизводительных микроконтроллеров (рис. 2) с различной периферией и опциями памяти (например, H8S/2238F с 256 Кб флэш-памятью и 16К RAM). Это делает семейство Н8S промышленным стандартом в телекоммуникационном оборудовании и весьма распростран╦нным в промышленности (например, в управлении двигателями, торговых автоматах и системах безопасности). Представители семейства используются в бытовой технике, например, в видеокамерах, фотоаппаратах и новейших моделях автомобильных радиопри╦мников. Совсем недавно H8S и H8/300H стали успешно использоваться в исполнении со встроенной CAN-шиной и в быстро растущей области применения смарт-карт, так как многие производные включают один или несколько последовательных интерфейсов, соответствующих IS07816. Рисунок 1. Развитие контроллеров серии H8

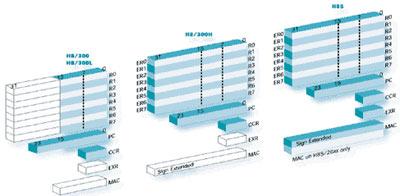

CPUВся серия Н8 обладает сходной архитектурой CPU. Архитектура, основанная на регистрах общего назначения, позволяет эффективно выполнять программы, написанные на С, и обеспечивает плотный код. Высокая плотность кода важна для сокращения необходимого объ╦ма памяти, что, в свою очередь, приводит к снижению стоимости системы и помогает исключить необходимость во внешней памяти. Как показано на рис. 3, 8-бит ряд Н8 имеет регистры с 16-бит разрядностью, а 16-бит ряд имеет регистры с 32-бит разрядностью, все они могут использоваться частично (например, побайтно). Н8S имеет дополнительный расширенный регистр кода условия (EXR) для улучшенного управления прерываниями, а Н8S/26XX - блок умножения с накоплением (как в DSP). Рисунок 3. Структура регистров

Микроконтроллеры семейства Н8S выполняют основные команды за один такт. Каждый регистр можно использовать для операции "указателя" или операции с данными. Архитектура позволяет использование любого из режимов адресации данных с любым регистром. Поскольку каждый регистр может использоваться как аккумулятор, индексный регистр или указатель адреса, вычисление адресов, выполняемое компилятором, может производиться чрезвычайно эффективно. Регистр ER7 используется как указатель стека, поэтому время доступа к данным стека чрезвычайно мало. В дополнение к регистрам общего назначения, предусмотрены два управляющих регистра: регистр кода условия (CCR) и сч╦тчик команд (РС). 8-бит CCR-регистр содержит все флаги CPU: переполнения, нуля, переноса, а также флаги прерываний. Набор командН8/300Н имеет набор команд, соответствующий общим требованиям программирования на языках высокого уровня (HLL). Он содержит 62 команды (табл. 1), в которых особое внимание уделяется арифметическим командам, операциям с адресами и поразрядной обработке данных. Более половины всех команд имеют длину 2 байт, что делает код очень компактным. Н8S обладает 69-командным набором, новые команды выделены жирным шрифтом. Таблица 1. Система команд для семейств H8/300H и H8S

По сравнению с CPU Н8/300, большинство команд переноса данных, логических, сдвига и арифметических операций усовершенствованы для работы с 16- и 32-бит данными. Новые команды, добавленные в Н8/300Н, включают умножение чисел со знаком, знаковое расширение, 16-бит команды ветвления и команды прерывания программы. В H8S набор команд ещ╦ более усовершенствован. Добавлены команды STM (store multiple) и LDM (load multiple). Они позволяют загрузить содержимое комбинированных регистров в стек, значительно сокращая время, по сравнению с командами PUSH и POP. Например, перенос содержимого 4-х регистров в стек занимает 40 тактов в Н8/300Н и только 11 - в H8S. Также улучшены некоторые битовые операции (для включения 16/32-бит абсолютной адресации) и операции сдвига для поддержки 2-бит сдвига. В H8S/26XX добавлены также команды для поддержки умножения c накоплением. Арифметические операцииДля выполнения комплексных алгоритмов, таких как цифровая фильтрация, контроллеры H8S и Н8/300Н снабжены мощными арифметическими командами, включающими сложение и вычитание 32-бит данных, умножение 16x16-бит данных и деление 32/16-бит данных. Операции умножения и деления возможны со знаками и без, что исключает необходимость обращения к специальным подпрограммам - библиотекам. В табл. 2 приведены сведения о скорости выполнения различных арифметических операций с тактовой частотой 16 (Н8/300Н) и 20 МГц (H8S). Таблица 2. Сравнение скорости выполнения команд для семейств H8/300H и H8S

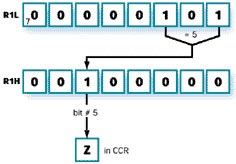

Побитовые операцииВ микроконтроллерных системах часто бывает необходимо обрабатывать данные побитно. Для решения таких задач H8S и Н8/300Н имеют 14 команд для побитовых операций, позволяющие программисту легко управлять битовыми данными. Возможно также выполнение операций булевой алгебры над битами, используя флаг переноса регистра CCR как битовый аккумулятор. В микроконтроллерных системах часто бывает необходимо выполнить переход к той или иной части программы, в зависимости от значения двух битовых флагов, расположенных в RAM или портах ввода/вывода. Используя логические операции, предусмотренные в H8S и Н8/300Н, первый бит может быть загружен в разряд флага переноса. Затем можно выполнять побитовые логические операции, используя второй бит. Дальнейшая последовательность будет сопровождаться переходом, зависящим от значения флага переноса. Особенность побитовых операций в H8S и Н8/300Н - это возможность косвенного битового выбора с использованием значения из регистра общего назначения в качестве указателя бита. Этот механизм изображ╦н на рис. 4.

Прерывание программыВ CPU H8S и Н8/300Н введена команда TRAPA. Она включает прерывание программы, переход к обслуживающей программе с использованием одного из четыр╦х векторов исключительных условий (TRAPA 0 - 3). Эта операция может использоваться для включения быстрых, эффективных вызовов часто используемых подпрограмм, таких как, например, планировщик. Команда TRAPA может также использоваться для вызова программы обработки ошибок. АдресацияДля поддержки систем с большой памятью линейное адресное пространство CPU H8S позволяет осуществлять прямой доступ по любому адресу во вс╦м 16-Мбайт адресном пространстве, используя 24-бит указатели адреса. Термин "Линейное адресное пространство" означает, что нет необходимости в установке указателей страницы и нет ограничений размера кодовых модулей или массивов и структур данных. Режимы адресацииДругой путь, при помощи которого архитектура CPU может поддерживать эффективность компилятора, состоит в обеспечении полного набора мощных и гибких режимов адресации. Для обеспечения максимальной эффективности компилятора CPU H8S и Н8/300Н обеспечивает восемь режимов адресации (табл. 3). Каждая команда может использовать подмножество возможных режимов. Поддерживая такие типы данных, как массивы и стеки, CPU обладает косвенной адресацией либо с последующим приращением, либо с предварительным уменьшением адреса. Эти режимы поддерживают данные в виде байта, слова или длинного слова (±1,2 и 4).

Эти режимы абсолютной адресации обеспечиваются использованием 8-, 16- или 24-бит адресов. Вс╦ 16-Мбайт адресное пространство доступно при использовании 24-бит адреса. Режимы абсолютной адресации с 8- и 16-бит адресами подразумевают, что верхний байт или слово адреса - это H▓FFFF или H▓FF, соответственно. Это обеспечивает эффективную адресацию для встроенной области вводов/выводов и RAM, которые находятся наверху адресной карты. Такие укороченные адреса значительно сокращают объ╦м кода при доступе к этим областям. Пониженное энергопотреблениеВ современной электронной промышленности низкое энергопотребление становится вс╦ более важной задачей. Кроме увеличения срока службы батарей, например, в мобильных телефонах, ноутбуках и электронных фотоаппаратах, снижение энергопотребления важно по следующим причинам:

Микроконтроллеры семейства H8S в значительной степени отвечают всем этим требованиям:

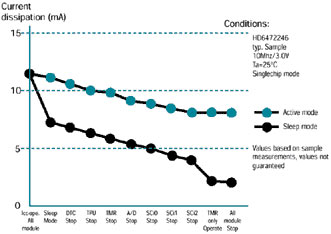

Рисунок 5. Снижение потребления энергии в зависимости от работающих переферийных модулей

Помимо возможности работы H8S при пониженной тактовой частоте, все H8S имеют возможность внутреннего динамического снижения частоты (частотной редукции). Некоторые изделия H8S характеризуются наличием 32-кГц субгенератора, который позволяет работать CPU, 8-бит и сторожевым таймерам на 32 кГц (субактивный режим) или только 8-бит и сторожевым таймерам (субдежурный режим) или, наконец, только сторожевым таймерам (дежурный режим). В дежурном режиме периодическое прерывание, создаваемое субгенератором с частотой, например, один раз в секунду, возвращает к работе CPU. CPU проверяет состояние системы (к примеру, нажатие клавиши) и затем активизирует другие модули или возвращается в режим ожидания, в зависимости от того, что требуется. Следовательно, может быть достигнуто очень низкое среднее значение потребляемой мощности даже с генератором реального времени, установленным программно. Если никакая работа не должна выполняться, а содержимое RAM должно сохраняться, микроконтроллеры H8S могут быть переведены в режим ожидания. В этом режиме генератор останавливается, и потребление мощности падает до уровня токов утечки (обычно, 0,01 мкА при комнатной температуре). Предусмотрены два режима: режим программного ожидания, который позволяет сохранить уровень сигналов в портах ввода/вывода, и режим аппаратного ожидания, который сохраняет только содержимое RAM, напряжение удержания RAM составляет всего 2 В. Некоторые из этих методов могут сочетаться для достижения минимальных средних значений потребляемой мощности, не мешая высокопроизводительной работе в обычном режиме. В качестве такой комбинации рассмотрим пример: предположим, что контроллер пересылки данных (DTC) должен использоваться для пересылки результатов преобразования из АЦП в буфер RAM (например, 64 байта). CPU не должно обрабатывать данные до окончания сбора всех данных. Этот сценарий позволяет отключить все модули, за исключением АЦП и DTC, и перевести CPU в режим ожидания во время пересылки. Результирующий ток будет примерно 3 мА при 10 МГц и 3 В Vcc. После окончания пересылки всех 64 байт, прерывание возвращает CPU к обработке данных. При этом программа может активизировать другие периферийные модули, если в том есть необходимость. Обратите внимание, что потребление мощности при этом сценарии может быть снижено дополнительно, если возможна работа на пониженной частоте генератора. Типовой ток Icc может быть от 2 до 3 мА. Контроллер прерыванийH8S характеризуется сложной системой прерываний, которая позволяет быстро реагировать на асинхронные события. В худшем случае, время отклика прерывания составляет 1,5 мкс для H8S (на 20 МГц). Поскольку почти каждый источник прерывания имеет свой собственный вектор, процедура обслуживания прерывания может немедленно начать выполнять самые необходимые действия, вместо того, чтобы опрашивать флаги состояний для обнаружения причины прерывания. Если два или более события, требующие прерывания, происходят одновременно, они принимаются и обрабатываются в порядке приоритета. Программные прерывания (Trap) доступны в любой момент выполнения программы. Прерывания обрабатываются следующим образом:

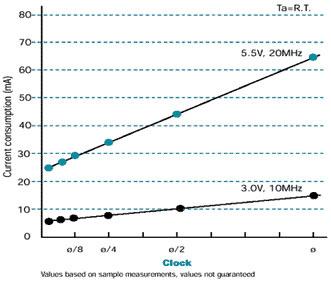

Внешние прерывания (NMI и IRQ)H8S имеет несколько внешних прерываний, включая одно немаскируемое (NMI). Оно может быть запрограммировано для активации либо по переднему, либо по заднему фронтам. Рисунок 6. Зависимость потребления тока от тактовой частоты

|

|

|

|

|

PDFs | Новости | Литература | Схемы | Форум | Блоги | Реклама |

16-бит микроконтроллеры фирмы HITACHI серии H8S. Часть 1.

16-бит микроконтроллеры фирмы HITACHI серии H8S. Часть 1.