|

Д. Чоловский 16-бит микроконтроллеры фирмы HITACHI серии H8S. Часть 2Микроконтроллеры HITACHI пользуются устойчивым спросом на европейском рынке. По итогам 1999 года компания Hitachi занимала на европейском рынке второе место по объ╦му продаж 16-бит микроконтроллеров, третье место по поставке 4-бит, шестое - по поставке 8-бит и второе место в мире по поставке 32-бит RISC-микроконтроллеров. Флэш-памятьТрадиционно сильной стороной микроконтроллеров Hitachi были и есть большая встроенная память и передовые технологии е╦ изготовления. Уже в течение многих лет важной стратегией является обеспечение поставляемых на европейский рынок микроконтроллеров с высокоскоростной, встроенной в кристалл флэш-памятью. В наши дни эта технология представлена в их третьем поколении и предлагает большие объ╦мы памяти и программирование на одном напряжении. Интегрирование большой и гибкой памяти дает потребителям массу преимуществ, некоторые из которых становятся решающими в современной электронной промышленности. Например, интеграция старой микроконтроллерной разработки, использующей внешние память и периферию, в однокристальную значительно снижает ЭМИ, так как адресные и информационные шины служат основным источником излучения в системе. Вместе с низким энергопотреблением микроконтроллеров фирмы Hitachi такая обновл╦нная конструкция часто моментально исключает проблемы, связанные с ЭМИ. В то же время, дорогостоящие меры по экранированию могут стать ненужными, таким образом стоимость системы снижается, и для платы требуется меньше места. Другие преимущества большой встроенной памяти и особенно встроенной в кристалл флэш-памяти:

Программирование флэш-памятиРежим начальной загрузкиВход в режим начальной загрузки происходит, если режимные выводы H8S находятся в определ╦нном состоянии после сброса. В режиме начальной загрузки выполнение программы начинается со скрытой ROM. Программа, записанная в этой ROM, инициализирует один из последовательных интерфейсов и загружает часть программы (поставляемой компанией Hitachi по желанию заказчика), которая позволяет программировать флэш-память. Режим начальной загрузки может использоваться для программирования нового устройства с флэш-памятью, даже если оно уже впаяно в печатную плату. Пользовательский режимПользовательский режим не вводится через режим сброса. Он аналогичен нормальной работе, но с программированием флэш-памяти, возможным через режимные вводы (обычно FWE). В пользовательском режиме внешнее переключающее событие заставляет пользовательскую программу скопировать часть программы в RAM. Основная программа переходит к выполнению этой части программы. Затем флэш-память может быть перепрограммирована под управлением пользовательского приложения, используя все ресурсы кристалла (то есть загрузка новой программы не обязательно должна использовать последовательный интерфейс, она может пользоваться другими источниками). Этот режим предназначен для обновления содержимого флэш-памяти. Режим PROMВсе варианты флэш-памяти H8S могут также программироваться с использованием программных средств для общего программирования, то есть таким же образом, как программируются однократно программируемые ПЗУ (ОТР). Рисунок 1. Временная диаграмма выборки данных из внешней памяти

Контроллер состояния шины (BSC)Поскольку одной из основных причин применения H8S и Н8/300Н является 16-Мбайт линейное адресное пространство, они часто используются в системах с большим объ╦мом внешней памяти. H8S и Н8/300Н поддерживаются мощным контроллером состояния шины (BSC), который позволяет подключать внешнюю память и/или периферию без связующих логических схем (в отдельных редких случаях с небольшим их количеством). Контроллер состояния шины (BSC) также помогает получить максимальную производительность внешних устройств, например, избегая задержек адресного декодирования там, где используется встроенная генерация выбора кристалла. BSC делит адресное пространство на 8 областей. Для каждой из них можно выбрать ряд атрибутов, например:

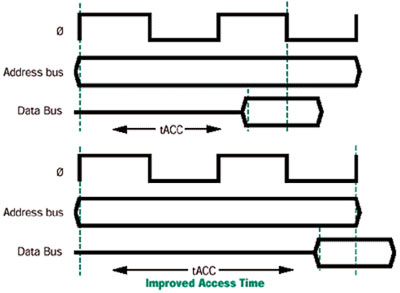

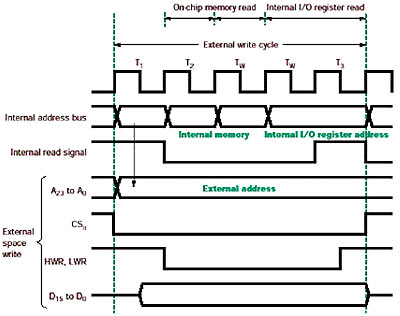

Контроллер состояния шины (BSC) в H8SОдно из основных преимуществ H8S перед Н8/300Н - это выполнение основных команд за один цикл синхронизации, что составляет всего 50 нс при 20-МГц генераторе, если они выполняются из внутренней памяти. Для того, чтобы снизить негативное влияние на быстродействие медленных внешних устройств, BSC имеет максимальную производительность и гибкость. Большая часть микроконтроллеров включает поддержку быстрой страничной DRAM (в H8S/26хх и в некоторых вариантах H8S/23хх), ROM с режимом пакетной обработки, буфер записи, который независимо выполняет выборку медленных внешних сигналов (в H8S/26хх и в некоторых вариантах H8S/23хх) и уменьшает время выборки чтения сигналов пут╦м сдвига фронта синхроимпульса, фиксирующего данные в конце цикла шины. Интерфейс DRAMНекоторые микроконтроллеры серий H8S/26хх и H8S/23хх могут работать непосредственно с DRAM, позволяя подключать до 8 МБ DRAM без каких-либо связующих логических схем. BSC выполняет адресное мультиплексирование (8, 9 или 10 бит), синхронизацию и позволяет использовать быстрый страничный режим. DRAM поддерживает режим автогенерации или CAS-before-RAS (CBR, режим регенерации опережающей подачей строба адреса столбца по отношению к стробу адреса строки). Для режима CBR-регенерации BSC обеспечивает независимый сч╦тчик, задающий цикл регенерации, поэтому нет необходимости использовать дополнительный таймер. Уменьшение времени выборки чтения сигналовДля того, чтобы дать внешним устройствам максимум времени для пересылки необходимых данных на шину, фронт выборки чтения, фиксирующий данные, сдвинут к концу выполнения цикла. Поэтому время выборки чтения сигналов уменьшилось примерно на одну четверть по сравнению с Н8/300Н. Буфер записи данныхВ H8S/26хх и в некоторых вариантах H8S/23хх предусмотрен буфер записи данных. Это позволяет CPU продолжать внутреннюю обработку данных, пока BSC независимо занимается выборкой медленной записи. Рис. 2 показывает пример временной диаграммы, когда используется буфер записи данных. Эта функция активизирована, если внешняя запись или одноадресная DMA-пересылка данных продолжается в течение 2-х тактов или более и есть следующая внутренняя выборка. В этом случае на первом такте выполняется только внешняя запись. Но со следующего такта и далее внутренняя выборка выполняется параллельно с внешней, не ожидая е╦ окончания. Рисунок 2. Работа буфера записи данных

Контроллер прямого доступа к памяти (DMAC)В системе с высокопроизводительным CPU и большой памятью контроллер прямого доступа к памяти значительно увеличивает быстродействие системы. Вместо того, чтобы тратить ресурсы CPU на пересылку данных между периферией и памятью, их можно практически полностью использовать для вычислений, пока происходит пересылка данных. В сочетании с другими периферийными устройствами, такими как таймеры, SCI или выходы TPC/PPG, работающие в режиме реального времени, может быть построена полностью автономная система, например, для управления шаговым двигателем, для связи с модулями жидкокристаллического дисплея (ЖКД) или клавиатурой без какого-либо участия CPU. Поскольку H8S почти утраивает быстродействие CPU, по сравнению с Н8/300Н, DMAC в H8S усовершенствован, по сравнению с DMAC в Н8/300Н для того, чтобы поддерживать в равновесии производительности CPU и DMAC. Общие характеристики контроллера прямого доступа к памяти:

Некоторые из основных усовершенствований в H8S:

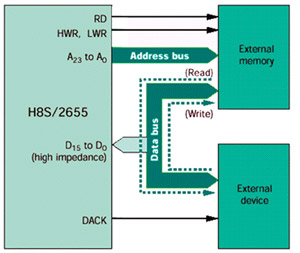

Режим короткого адресаВ этом режиме или адрес источника, или адрес назначения ограничивается 16 битами (H8S), где старшие разряды автоматически устанавливаются в логическую "1". Это позволяет выбрать внутренние входые/выходные регистры. Другие адреса имеют разрядность в 24 бит, так что доступно вс╦ адресное пространство. В режиме короткого адреса существуют: режим "IO mode" (режим входа/выхода, названный последовательным режимом в H8S), где полный адрес может автоматически увеличиваться или уменьшаться, "idle mode" (холостой режим), где полный адрес фиксирован, и "repeat mode" (режим повторения), позволяющий автоматическую пересылку содержимого буферов циклических данных. Буферы циклических данных используются во многих системах, например, для вывода управляющей последовательности на шаговый двигатель. Режим полного адресаДля выполнения пересылки между различным устройствами памяти может использоваться полный адрес. Здесь адреса источника и места назначения имеют 24-бит длину, и поэтому пересылка от памяти к памяти может быть выполнена между любыми областями всего 16-Мбайт адресного пространства. Этот режим позволяет или одиночную пересылку по запросу (нормальный режим), или пересылку блока данных (режим блочной пересылки). В "нормальном режиме" и с разреш╦нным "автозапросом" DMAC может быть установлен в монопольный режим, принимая от процессора на себя управление шиной до завершения пересылки, или в режим циклического захвата, где процессор и DMAC используют шину совместно. Режим одиночного адреса (H8S)Рис. 3 иллюстрирует новый режим одиночного адреса. В н╦м пересылка данных осуществляется непосредственно между шинами данных двух внешних устройств, например, внешнего периферийного устройства и DRAM. Преимуществом является скорость передачи, так как данные пересылаются за один цикл без временного хранения. Либо источник либо устройство назначения должны быть устройством, которое можно выбрать только стробом, используя вывод DACK. Адресная шина используется для доступа к другому ресурсу. Рисунок 3. Режим одиночного адреса

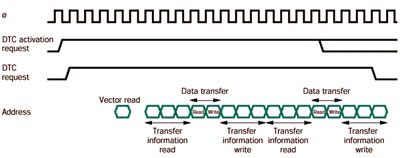

Контроллер пересылки данных (DTC)Анализ многих систем, использующих DMAC, показывает, что их значительная часть не требует максимальной скорости пересылки данных. Эти системы используют DMAC, главным образом, для снижения непроизводительных затрат центрального процессора, позволяя ему использовать свою производительность для вычислений. Поэтому в микроконтроллерах фирмы Hitachi предусмотрено другое периферийное устройство для автономной пересылки данных - контроллер пересылки данных (DTC). DTC предназначен для разгрузки CPU от задач пересылки данных, обеспечивая при этом максимальную гибкость. В отличие от DMAC, DTC может управлять большим количеством передающих каналов, и пересылка может осуществляться по запросу почти любого из периферийных устройств, которое может запросить прерывание, что можно сделать и программным пут╦м. С другой стороны, пересылка DTC примерно в 5 раз медленнее, чем пересылка DMA (например, 1000 нс против 200 нс на 20 МГц с источником - периферийным устройством и назначением - памятью). В режиме блочной пересылки непроизводительные затраты DTC разделяются рядом команд пересылки в блоке, таким образом практически исключая результаты непроизводительных затрат. Одиночное переключение может также запросить множественную пересылку (цепочечный режим). Эта особенность может использоваться, например, для пересылки результата аналого-цифрового преобразования в кольцевой буфер в RAM с последующим автоматическим перепрограммированием АЦП для выполнения других преобразований. Если задания для АЦП хранятся в таблице в ROM, которая используется DTC в циклической схеме, то пока результаты преобразования сохраняются в соответствующем количестве кольцевых буферов в RAM, DTC и АЦП могут выполнять другие совершенно различные задачи без какого-либо вмешательства CPU. На рис. 4 показана временная диаграмма такой цепочечной передачи. Обратите внимание, что один цикл генератора составляет всего 50 нс на 20 МГц. Как видно, вектор DTC читается после запроса пересылки только за один цикл, каждое перемещение пересылаемой информации между RAM DTC и регистрами DTC занимает 3 цикла, и пересылка данных занимает 2 цикла (минимум). Рисунок 4. Временная диаграмма работы блока DTC

DTC может рассматриваться как DMAC только при одном канале. Регистры для адресов назначения и источника, для режима пересылки и подсч╦та пересылки в действительности существуют только в единственном числе. Однако, эти регистры загружаются информацией, которая должна использоваться для пересылки из RAM. Это означает, что структура регистров DTC отображается в специальной RAM DTC столько раз, сколько существует каналов передачи, число которых выбрано разработчиком. Каждая пересылка может иметь разрядность байта или слова; адреса источника и устройства назначения должны иметь 24-бит разрядность (то есть охватывать весь диапазон адресов). Адреса источника и устройства назначения могут быть либо увеличивающимися, либо уменьшающимися (на 1 или 2) или фиксированными. Прерывание CPU может осуществляться запросом на прерывание, которое переключает передачу DTC или после каждой пересылки или после определ╦нного числа выполненных пересылок. ТаймерОдно из наиболее важных периферийных устройств любого микроконтроллера - блок таймера. В электронных системах таймеры используются по-разному. Они переключают задачи в системах, работающих в режиме реального времени, корректируют программные часы реального времени, управляют двигателями переменного и постоянного тока, шаговыми двигателями, проверяют соответствие внешних сигналов (тайм-аут), подсчитывают импульсы, например, от квадратурного шифратора, и делают многое другое. Таймеры могут работать даже как точные цифро-аналоговые преобразователи (DAC), если используются в качестве широтно-импульсных модуляторов. Для того, чтобы аккумулировать все эти применения, компания Hitachi разработала 2 мощных и гибких блока таймеров для своих 16-бит микроконтроллеров, а также несколько таймеров специального назначения, например, отдельные ШИМ-таймеры, сторожевые таймеры (WDT), таймеры поддержки низкоэнергетического режима и т. п. Блок таймера (TPU) в H8S - 6-канальный 16-бит с 16 выводами сравнения и захвата. Исключение - устройства H8S/21хх. Они предназначены для недорогих систем, где расширенная функциональность таймеров ITU/TPU или не нужна, или может быть заменена высокоскоростным CPU H8S. H8S/21хх имеют 16-бит независимый таймер (FRT) с 4 входами захвата и 2 выходами сравнения, а также 3 8-бит таймера. Предусмотрены отдельный 14-бит ШИМ и 2 сторожевых таймера (один с 32-кГц субгенератором). Блок импульсного таймера (TPU)Блок используется во всех устройствах H8S, при этом H8S/224х и H8S/222х имеют половинный состав TPU. Он состоит из 6 16-бит каналов таймера с 16 общими регистрами таймера (TGR), каждый из которых может выполнять задачи сравнения и захвата. Отдельные TGR могут также работать как буферные регистры для снижения нагрузки по прерываниям, которая приходится на CPU. Для каждого канала программно выбираемым источником входных сигналов может являться один из восьми источников. Возможным источником могут являться внутренние тактовые генераторы, сигналы внешних генераторов или другие таймеры, при этом последние эффективно обеспечивают каскадный метод соединения двух 16-бит таймеров в один 32-бит. TPU предлагает 4 канала для фазового сч╦та. Кроме того, TPU разрешает переключать А/Ц преобразование и может переключать пересылку данных, выполняемую контроллером пересылки данных (DTC). TPU позволяет генерировать 15-фазный ШИМ-сигнал, используя один TGR в качестве циклического регистра, а другие 15 - для установки режима. TPU не поддерживает дополнительный 6-фазный ШИМ-режим и 6-фазный ШИМ-режим синхронизированного сброса. 16-бит независимый таймер (FRT)Основной блок таймера H8S/21хх - 16-бит независимый таймер (FRT) с 2 выводами выходного сравнения и 4 - входного захвата. Устройство входного захвата может также работать в буферном режиме, тогда только 2 вывода выходного сравнения выполняют свои прямые функции. Входная синхронизация может осуществляться от одного из 3 внутренних источников или от внешнего источника, при этом также возможен подсч╦т событий. FRT характеризуется одним независимым прерыванием для каждого вывода сравнения/захвата и одним при переполнении. 8-бит таймерыСерии H8S/2655, H8S/2355 и 53, H8S/224х, H8S/234х и H8S/21хх имеют дополнительный 8-бит таймер с двумя каналами (TMR0 и TMR1). Каждый канал имеет два регистра с временными константами (TCORA и TCORB), которые постоянно сравниваются со значением сч╦тчика для определения совпадения. 8-бит модуль таймера может выполнять различные функции, включая импульсный выход с произвольным коэффициентом заполнения или сч╦т событий на внешнем входе. 8-бит таймер имеет следующие характеристики:

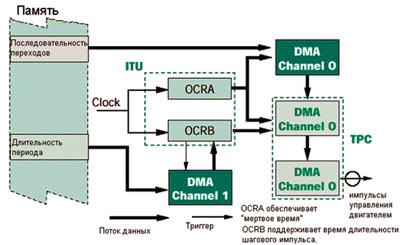

Эти 8-бит таймеры могут использоваться для поддержки минимального уровня работоспособности таймера в периоды нахождения системы в режиме ожидания. Результатом является, с одной стороны, низкое энергопотребление, так как TPU может отключаться в этой ситуации, и с другой стороны, минимальная активность таймера. 8-бит таймер может использоваться, например, для коррекции программной синхронизации в режиме реального времени или для сканирования клавиатуры, так что система может вернуться в режим полной активности при нажатии клавиши. Расширенные 8-бит таймеры в H8S/21ххМикроконтроллеры H8S/21хх характеризуются 8-бит модулем таймера, аналогичным описанному выше. Также существует третий 8-бит канал таймера TMRY, который обладает сходными функциями с TMR0 и TMR1, но без устройства проверки совпадения значений. 14-бит ШИМ-таймерH8S/21хх снабж╦н двухканальным ШИМ-таймером, предназначенным для использования в качестве цифро-аналогового преобразователя. Он базируется на 14-бит сч╦тчике, генерируя аналоговые сигналы с 14-бит разрешением и малой пульсацией. Сторожевой таймер (WDT) в Н8SТаймер имеет WDTOVF-вывод, который может сигнализировать о переполнении сторожевого таймера внешним устройствам. Он может работать с гораздо более медленными источниками тактовых импульсов, с частотой до f/131072, которая обеспечивает до 1,68 с (на 20 МГц) между сбросами сторожевого таймера до наступления его переполнения. Сторожевой таймер (WDT), работающий от 32-кГц субгенератораВ некоторых вариантах Н8S установлен второй WDT, который работает от 32-кГц субгенератора. Этот субгенератор может делить частоты на 2 и так далее до 256 до того, как он будет использован в качестве входного тактового генератора для сч╦тчика. Следовательно, конечная частота переполнения может равняться 32 кГц, деленным на 256x256 = один раз каждые 2 секунды. Этот WDT может использовать для своего сброса прерывание, сброс или NMI. При запросе прерывания WDT полезен для коррекции программной синхронизации в режиме реального времени. Для этого применения каждый периферийным модуль устройства выключается, и CPU переходит в режим ожидания. Затем WDT возвращает CPU к работе, например, каждую секунду, CPU обновляет программные регистры генератора реального времени (обычно находящиеся в RAM) и снова переходит в режим ожидания, если нет другой работы. Контроллер последовательности импульсов таймера (TPC)Программируемый импульсный генератор (PPG)Эти периферийные устройства позволяют генерировать выходные цифровые сигналы, синхронизированные с частотой таймера, так что они могут рассматриваться как "выходные сигналы реального времени". Такая, управляемая таймером, выходная цифровая система может генерировать постоянный поток данных, которые появляются на выводах контроллера точно в пределах интервалов, на которые запрограммирован таймер, без какого-либо "дрожания", вызываемого, например, задержками обработки прерывания в системе, где процедура обработки прерывания управляет через выводы контроллера. TPC и PPG могут обеспечивать это без вмешательства CPU, если используются вместе с DMA. TPC и PPG снабжены регистрами, называемыми "регистрами следующих данных". Данные этих регистров пересылаются под управлением таймера в "регистры данных порта" (то есть на контакты). У CPU, DMA или DTC (там, где применяется) оста╦тся время до следующей отметки таймера скопировать следующее значение из таблицы данных из памяти в "регистр следующих данных". Этот механизм работает независимо для четыр╦х групп по 4 контакта каждая, так что всего таким образом может управляться 16 контактов. TPC и PPG предназначены прежде всего для управления шаговыми двигателями при незначительном вмешательстве CPU в этот процесс. Однако, они могут использоваться и для множества других целей. Например, очень легко генерировать поток последовательных данных, если нужен дополнительный последовательный интерфейс. Возможно даже управление модулем ЖКД без использования какого-либо контроллера синхронизации ЖКД, таким образом исключается вся периферийная ИС в микроконтроллерной системе, которая должна подключаться к модулю ЖКД. Управление шаговым двигателем при помощи ТРСНа рис. 5 показано, как можно выполнить управление шаговым двигателем, используя ITU, TPC и DMAС. В этом примере однофазный шаговый двигатель управляется при помощи транзисторов, соедин╦нных по мостовой схеме. Поэтому необходимо обеспечить время задержки между переключениями фаз во избежание короткого замыкания. Рисунок 5. Управление шаговым двигателем

Отметки совпадения результатов сравнения от ITU используются для включения DMAC, на ТРС пода╦тся новая последовательность импульсов. Эти данные представляют собой последовательность управления следующей фазой и хранятся в таблице памяти. DMAC использует память для пересылки этих данных при каждой отметке совпадения. ТРС также использует сигналы от ITU для пересылки содержимого NDR в порт. Используя режим ТРС там, где в порту производится переключение из 0 в 1 (то есть переключение фазы) только при отметке совпадения А, вводится время задержки, равное значению GRA. При управлении шаговым двигателем обеспечение фазовой последовательности импульсов на контактах порта - только часть задачи. Необходимо также изменять время между последовательностями на выходе, чтобы обеспечить ускорение или замедление двигателя. Когда ТРС, ITU и DMAC работают вместе, моменты ускорения, замедления и постоянной скорости могут регулироваться при минимальной нагрузке на CPU. Оно нужно только тогда, когда производится переключение из одной фазы в другую. Это достигается подключением второй схемы памяти к каналу ввода/вывода DMAC для перезагрузки регистра сравнения таймера после пересылки на выход каждой новой последовательности импульсов. DMAC может выбрать данные для нового шага из таблицы значений, сохраняемой в памяти системы. Поэтому при использовании таблицы увеличивающихся и уменьшающихся значений можно замедлять и ускорять двигатель без вмешательства CPU. |

|

|

|

|

PDFs | Новости | Литература | Схемы | Форум | Блоги | Реклама |

16-бит микроконтроллеры фирмы HITACHI серии H8S. Часть 2.

16-бит микроконтроллеры фирмы HITACHI серии H8S. Часть 2.