|

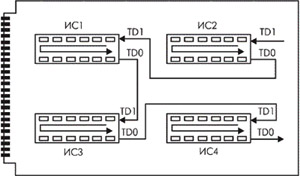

В. Рустинов, А. Городецкий ╚Разделяй и властвуй╩ - принцип граничного сканированияCо времени опубликования в 1990 году стандарта IEEE 1149.1/JTAG, технология граничного сканирования (Boundary Scan - BS) утвердила себя как незаменимый инструмент при тестировании устройств c ограниченным доступом к выводам ИС. Широкое применение многослойных печатных плат с ИС в корпусах, изготовленных по технологиям BGA, COB и QFP, дало новый мощный импульс развитию и повсеместному применению этой технологии. Граничное сканирование используется также как средство доступа к внутренним регистрам микросхем для наблюдения за их состоянием в процессе отладки. ВведениеИсключительно широко технология BS применяется также для внутрисхемного программирования (On-board programming - OBP), одним из направлений которого является внутрисистемное программирование (ISP - In-System Programming). Под термином ISP обычно понимают внутрисхемное программирование установленных на плату интегральных схем ПЛИС (CPLD, FPGA), а собственно термин OBP относится к внутрисхемному программированию ИС флэш-памяти и ЭCППЗУ (EEPROM). В 1996 году была создана рабочая группа IEEE по разработке нового стандарта по ISP. Основная задача группы за-ключалась в разработке документа, который бы определял стандартный процесс и методологию реализации внутрисистемного программирования, базирующихся и согласованных с протоколом стандарта IEEE 1149.1. В 2000 году был утвержд╦н новый стандарт IEEE P1532 Boundary-Scan-Based In-System Configuration of Programmable Devices. Для удовлетворения растущих потребностей инженеров в использовании этих технологий на мировом рынке успешно работают несколько компаний, предлагающих широкий спектр автоматизированного инструментария на основе ПК. Уже сейчас простейший программно-аппаратный комплекс BS можно купить за 2√3 тыс. долл. США. По оценкам экспертов, к 2004 году рынок применений технологии BS вырастет в 5 раз и превысит рубеж 400 млн. долл. в год. Если обратная связь с читателями подтвердит интерес к данной тематике, то авторский коллектив, совместно с редакцией, планирует подготовить цикл статей, отражающих современное состояние методов тестирования и внутрисхемного программирования, базирующихся на принципах граничного сканирования, реализацию этих методов на уровне систем, плат и отдельных микросхем, включая самые современные и сложные ИС типа SoC (System-on-Chip). Будут подвергнуты детальному анализу отличия в подходах и применяемых средствах к реализации методов BS при разработке программ тестирования и внутрисхемного программирования и на этапе их применения при крупносерийном производстве электронных систем. В статьях цикла будут рассмотрены основные принципы и практические вопросы реализации тестопригодного проектирования электронных систем и разработки тестовых программ, отражающие опыт авторов в этой области. Цель этой статьи - помочь разработчику, стоящему на пороге освоения новой технологии BS, разобраться с основными направлениями использования граничного сканирования и тенденциями его развития, а также выбрать верный путь решения стоящих перед ним задач. Еще раз об основахВ этом разделе мы лишь вкратце остановимся на основах технологии граничного сканирования, поскольку на эту тему существует большое количество публикаций в отечественной [1-3] и зарубежной [4-6] печати. Стандарт IEEE 1149.1/JTAG определяет очень простую шину с несложным протоколом. Шина может применяться иерархически на всех используемых сегодня уровнях - от ИС до системы, состоящей из нескольких отдельных печатных плат и/или модулей. Для этого достаточно на каждом уровне соединить друг с другом в единую цепочку все элементы, в которых заложена аппаратная избыточность, обеспечивающая граничное сканирование. В дальнейшем такие элементы будем называть совместимыми с 1149.1 - BS-элементами. Как показано на рис. 1, все 1149.1 BS-ИС на плате соединяются друг с другом так, чтобы выход TDO предыдущей микросхемы был соедин╦н со входом TDI следующей. Рисунок 1. Организация пути сканирования на плате (BS-цепочка)

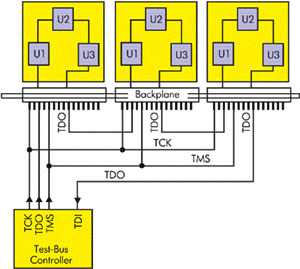

На уровне системы TDO предыдущей печатной платы может быть соедин╦н с TDI последующей платы, как показано на рис. 2. Следует подчеркнуть, что это лишь один из возможных вариантов применения граничного сканирования на уровне системы, самый простой и безо всякой аппаратной избыточности. В дальнейшем будут подробно рассмотрены более сложные и существенно более эффективные методы объединения локальных BS-цепочек. Рисунок 2. Один из возможных вариантов организации пути сканирования в системе

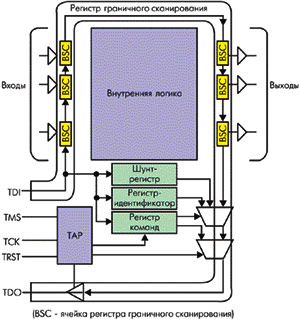

Принцип граничного сканирования заключается в размещении последовательного сдвигового регистра (BS-регистра) по границам 1149.1 BS-микросхем, прич╦м сами ячейки такого регистра располагаются непосредственно между внешними выводами и функциональным ядром этих микросхем. К каждой ИС добавляются всего лишь 4 (иногда 5) внешних вывода контакта: TDI (Test Data In - вход тестовых данных), TDO (Test Data Out - выход тестовых данных), TMS (Test Mode Select - выбор тестового режима) и TCK (Test Clock - тестовая синхронизация). К внешнему разъ╦му каждой платы добавляются эти же 4 внешних вывода. Стандарт IEEE 1149.1/JTAG предусматривает также необязательный пятый внешний вывод TRST (асинхронный сброс). На самом нижнем уровне этой иерархии находится 1149.1 BS-микросхема, внутренняя структура которой показана на рис. 3. Согласно стандарту IEEE 1149.1, к каждому выводу ИС подсоединена специальная схема, состоящая из 2 триггеров и 2 мультиплексоров, обеспечивающая два режима функционирования - нормальный, то есть штатный, и режим тестирования. С помощью тестовой шины стандарта IEEE 1149.1 можно управлять этими логическими ячейками. Вообще-то BS-ячейка может работать и в обычном режиме ИС, и это одна из основных идей BS. Рисунок 3. Внутренняя организация 1149.1-микросхемы

Стандарт IEEE 1149.1 различает 4 основных элемента BS-структуры, каждый из которых размещается на BS-ИС [4]:

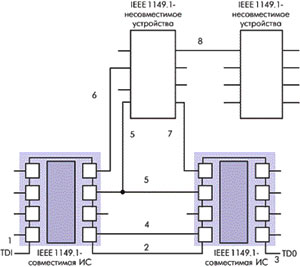

Первые три элемента BS-структуры, а также BS-регистр и шунт-регистр являются обязательными, ими снабжены все BS-ИС, остальные регистры данных необязательны. Управление одноразрядными ячейками BS-регистра осуществляется ТАР-контроллером в функции команд, поступающих в последовательном коде на вход TMS и стробируемых нарастающим фронтом синхроимпульсов TCK. В зависимости от выбранной ТАР-контроллером команды, каждая BS-ячейка граничного сканирования может либо принимать поступающий на вход Data In бит данных во входной триггер, либо выдавать содержимое триггера на выход Data Out, либо последовательно сдвигать бит данных от входа Scan In к выходу Scan Out в пределах BS-регистра, передавать бит данных от входа Scan In к выходу Data Out, а также либо передавать бит данных напрямую от Data In к Data Out. Эта маршрутизация выполняется входным и выходным мультиплексорами, непосредственно управляемыми ТАР-контроллером. Если на цифровой плате установлены только сканируемые микросхемы (что случается нечасто), то в этом случае отпадает необходимость применять внутрисхемное тестирование для выполнения диагностических процедур. Фактически, с помощью технологии BS появляется возможность упростить многие задачи, "разрезав" схему на отдельные кусочки меньших размеров. Так, технология граничного сканирования позволила применить в электронике принцип "разделяй и властвуй". Однако практика - упрямая вещь, и вряд ли найд╦тся такой разработчик, который сможет построить полностью сканируемую цифровую плату или систему. Причины очевидны. Во-первых, многие производители микросхем и сегодня выпускают цифровые ИС, не поддерживающие стандарт IEEE 1149.1. Кроме того, на подавляющем большинстве современных электронных плат устанавливаются аналоговые микросхемы и пассивные элементы. Не стоит отчаиваться, поскольку вс╦ равно и в этом случае существует возможность тестировать платы и системы, используя технологию BS. В этом случае, как показано на рис. 4, только 1149.1-микросхемы BS-ИС соединяются так, чтобы организовать путь сканирования на плате, не затрагивая при этом остальные пассивные и активные элементы. Конечно, в этом случае полнота покрытия неисправностей будет ниже, чем в полностью сканируемой плате, и будет сильно зависеть от соблюдения разработчиком платы правил и принципов тестопригодного проектирования. Рисунок 4. Частично сканируемая плата

Программно-аппаратные комплексы граничного сканированияДля того, чтобы получить максимальную отдачу от использования технологии граничного сканирования, необходим универсальный и доступный инструментарий. За последние 10 лет ряд компаний в Европе и США производят программно-аппаратные комплексы на базе ПК, предназначенные для разработки и применения программ тестирования и внутрисхемного программирования на базе технологии граничного сканирования. В табл. 1 приведены сведения о наиболее известных компаниях. В отч╦те калифорнийской исследовательской группы Electronic Trend Publications за 2000 год отмечено, что компания ASSET Inter-Tech с их комплексом ScanWorks заняла ведущее место на мировом рынке BS-комплексов. Эта фирма значительно опередила конкурентов на североамериканском рынке (43% мирового рынка) и широко представлена также на европейском рынке BS-комплексов (39% мирового рынка). Таблица 1. Производители программно-аппаратных комплексов граничного сканирования

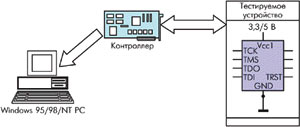

Все эти компании производят широкую гамму портативных, недорогих компьютеризованных систем разработки и применения программ тестового диагностирования и внутрисхемного программирования с использованием технологии граничного сканирования. Как показано на рис. 5 и 6, они базируются на ПК, который соединяется с тестируемым и/или программируемым устройством либо через интерфейсную плату, либо непосредственно через параллельный порт компьютера. Рисунок 5. Программно-аппаратный комплекс граничного сканирования на базе ПК

Рисунок 6. Типичное разбиение на фрагменты для граничного сканирования современной платы

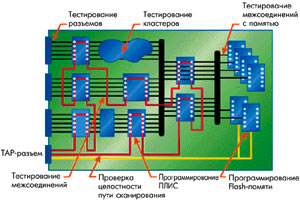

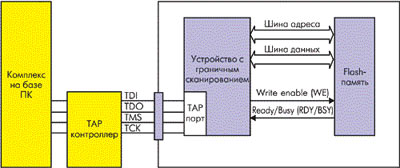

Программное обеспечение таких комплексов позволяет разрабатывать и применять программы как для поиска и диагностирования неисправностей различных классов, так и для внутрисхемного программирования. Предварительно в систему необходимо ввести некоторые исходные данные: описание BS-ИС, описание пути сканирования и описание тестируемой платы (модуля, системы) в целом. Описание каждой BS-ИС зада╦тся присущим ей BSDL (Boundary Scan Description Language) файлом на все сканируемы элементы, которые установлены на плате. В этих файлах содержится информация о том, какова структура граничного сканирования данной ИС, организован путь сканирования в элементе и какие функции, определ╦нные стандартом 1149.1, она поддерживает. Производители BS-ИС бесплатно обеспечивают пользователей этими файлами. В табл. 2 содержится информация о месте хранения BSDL-файлов различных производителей ИС. Таблица 2. Размещение в интернете BSDL-файлов различных производителей Затем вводится информация о том, как соединены между собой все элементы, установленные на плате (netlist). Обычно файл с таким описанием может быть введ╦н в любом из существующих форматов САПР печатных плат. И, наконец, с помощью специального языка HSDL (Hierarchical Scan Description Language) описывается путь сканирования на плате (BS-цепочка). После этого схема платы разбивается на отдельные фрагменты. Каждый такой фрагмент представляет схемную структуру, тестирование которой выполняется с использованием определ╦нного подхода. На рис. 6 показаны результаты такого разбиения типичной современной платы. Идеальной является структура, состоящая из линий, входы и выходы которых соединены со сканируемыми элементами, и никакие другие элементы к этим линиям не подключены. В таких схемных структурах технология граничного сканирования позволяет обнаружить все неисправности, вызванные обрывами линий и замыканиями между ними, а также все константные неисправности на этих линиях и неисправности, проявляющие себя как константные. В тех случаях, когда линии схемы неконтролируемы (или частично контролируемы) через сканируемые элементы, полнота покрытия неисправностей существенно ниже. Очевидно, что полнота покрытия неисправностей зависит от обеспечения показателей управляемости и наблюдаемости на линиях схемы со стороны сканируемых элементов BS-ИС. Вот почему для эффективного использования технологии BS разработчикам схем так важно владеть принципами и методами тестопригодного проектирования. Рассмотрим вкратце отдельные возможные этапы применения технологии граничного сканирования. Проверка целостности пути сканированияЭто, в сущности, самотестирование структуры граничного сканирования. На рис. 4 это линии 1, 2 и 3. Кроме того, на этом этапе проверяется отсутствие неисправностей (обрывы, замыкания, константные дефекты) на линиях сигналов TCK, TMS и TRST. Тестирование межсоединенийСуществующие алгоритмы тестирования межсоединений дают хорошие результаты как для обнаружения, так и для локализации неисправностей типа обрыва или замыкания линий, а также константных неисправностей в схемных структурах, которые начинаются и заканчиваются сканируемыми элементами. На рис. 4 это линии 4 и 5. Для проверки целостности соединений разъ╦мов со сканируемыми элементами достаточно предусмотреть специальные технологические кабели, которые соединяют внешние выходы со входами. Определ╦нные трудности возникают при тестировании соединений между сканируемыми и не сканируемыми элементами, как например, линии 6, 7 и 8 на рис. 4. Полнота покрытия неисправностей в таких случаях зависит от того, как определены соответствующие выводы сканируемых и не сканируемых элементов (входы, выходы, входо-выходы с возможностью перевода в третье состояние и так далее) и в какой степени возможно исключение (или уч╦т) влияния остальной схемы на данные линии (общие шины, объедин╦нные выходы, "прозрачные" буферы и резисторы, подключенные к питанию или "земле" резисторы и так далее). Такие ситуации требуют детального анализа, и лучше, если он выполняется на этапе тестопригодного проектирования схемы, а не на этапе тестирования готовой платы. В конечном сч╦те, низкая управляемость и наблюдаемость в таких схемных структурах приводит к тому, что тесты обладают невысокой полнотой покрытия неисправностей. В последующих публикациях более подробно будет показано, как решаются эти проблемы. Тестирование межсоединений с памятьюНа этом этапе с помощью сканируемых элементов в память записываются, а затем из не╦ считываются тестовые данные (рис. 6). Тест для обнаружения обрывов и замыканий между линиями, а также константных неисправностей и неисправностей, проявляющих себя как константные, обычно представляет собой прямой и обратный "шахматный код" с некоторыми модификациями. Тестирование кластеровКластером называется схемная структура, состоящая из несканируемых элементов, входы и выходы которой соединены со сканируемыми элементами. С их помощью на кластер подаются тестовые воздействия и регистрируется их реакция. Тесты для кластеров в подавляющем большинстве случаев пишутся вручную на специальном макроязыке. Такие тесты разрабатываются относительно тех же классов неисправностей, что и тесты межсоединений. Внимательный читатель, конечно, заметил, что среди неисправностей, которые могут быть обнаружены при помощи технологии граничного сканирования, не встречаются функциональные неисправности. Это не случайно, так как эта технология, в общем случае, не предназначена для реализации функционального тестирования, являясь (наряду с зондовым внутрисхемным тестированием, известным как ICT - In-Circuit Testing) важнейшей составной частью структурного тестирования. Тем не менее, в отдельных случаях технология граничного сканирования может быть применена и в некоторых функциональных тестах ИС, предусматривающих подобное тестирование. Внутрисхемное программированиеКак было указано выше, внутрисхемное программирование установленных на плату интегральных схем подразделяется на внутрисистемное программирование (ISP) ПЛИС (CPLD, FPGA), а собственно термин OBP относится к внутрисхемному программированию ИС флэш-памяти и ЭCППЗУ (E2PROM). Отличие между этими двумя подходами определяется самой структурой двух указанных групп ИС памяти: ПЛИС всегда являются сканируемыми ИС, тогда как ИС флэш-памяти и ЭCППЗУ таковыми не являются никогда. В соответствии с этим отличием, программирование ПЛИС (ISP) осуществляется при помощи их самих, как бы изнутри (рис. 6), и для этого никакие другие BS-ИС не нужны. Для программирования ПЛИС по цепям граничного сканирования должен быть подготовлен специальный ПВФ файл (последовательный векторный формат, SVF - Serial Vector Format), стандарт которого совместно разработан в 1991 году фирмами Texas Instruments и Teradyne. ПВФ представляет собой стандартный текстовый файл для записи тестовых векторов (входных воздействий и ожидаемых реакций) и масок для их последовательного ввода по цепям граничного сканирования. Любой из упомянутых выше программно-аппаратных комплексов граничного сканирования позволяет автоматически получать ПВФ-файлы на основе исходного файла программирования ПЛИС в любом формате, а также осуществляет сам процесс внутрисистемного программирования установленного на плату ПЛИС. ИС флэш-памяти и ЭCППЗУ, не являясь BS-ИС, нуждаются для реализации их внутрисхемного программирования в окружении других BS-ИС, при помощи которых и реализуется процесс их программирования (рис. 6). Это совершенно другой процесс, не требующий применения ПВФ-файлов, однако нуждающийся в разработке программ внутрисхемного программирования на специальном макроязыке, позволяющем описать конкретное окружение данной ИС памяти в данной плате и конкретные особенности процессов записи/чтения данного типа ИС памяти. Подготовка адекватного окружения предназначенных для внутрисхемного программирования ИС флэш-памяти и ЭCППЗУ является одним из важнейших этапов тестопригодного проектирования плат. Обычно под этим термином понимается программирование флэш-памяти, CPLD, FPGA и E2PROM, которые уже установлены на плату, с помощью сканируемых элементов, также находящихся на этой плате. В качестве примера, на рис. 7 показан принцип внутрисхемного программирования флэш-памяти с помощью граничного сканирования BS. Рисунок 7. Внутрисхемное программирование флэш-памяти

Применение внутрисхемного программирования ISP имеет следующие преимущества:

Для того, чтобы успешно применять внутрисхемное программирование, необходимо всегда помнить, что программирование микросхем осуществляется непосредственно внутри собранной платы. Нужно тщательно продумать взаимодействие этих микросхем с другими элементами системы в режиме программирования и в рабочем режиме, а также учитывать влияние окружающей схемы логики. Влияние граничного сканирования на развитие новых технологийСегодня становится очевидным, что граничное сканирование означает гораздо больше, нежели только тестовое диагностирование и внутрисхемное программирование. Поскольку BS позволяет организовать доступ к аппаратным структурам внутреннего сканирования и встроенного самотестирования (BIST - Built-In Self-Test), команды INTEST и RUNBIST становятся обычными для сложных заказных СБИС и ПЛИС. Кроме того, бурно развиваются несколько новых направлений, в основу которых были положены идеи и принципы граничного сканирования. Так, ещ╦ в начале 90-х годов была сформирована группа для разработки стандарта IEEE 1149.4 Mixed-Signal Test Bus Standard. В н╦м определены правила доступа к выводам аналоговых элементов для подачи аналоговых и цифровых воздействий и получения реакций в цифровом и аналоговом видах [5]. В 1999 году данный стандарт был утвержд╦н, и несколько компаний уже активно готовят к выпуску продукцию, которая его поддерживает. Массовое появление на рынке ИС со встроенными механизмами аналогового и гибридного граничного сканирования произвед╦т подлинный переворот в современной электронике, и мы находимся на пороге этого события. Принципы граничного сканирования находят сво╦ применение и в тестировании систем на кристалле (SoC). Под SoC понимается система с шинной организацией, которая состоит из нескольких сложных элементов: ядра, встроенной памяти и связующей логики. Тестирование таких систем является чрезвычайно сложной задачей, существенно более сложной, чем тестирование микропроцессоров. Е╦ решение возможно только при использовании структурных методов тестопригодного проектирования [6]. В 1995 была создана рабочая группа IEEE по разработке стандарта IEEE P1500 Embedded-Core Test Standard. Основная деятельность этой группы была направлена на создание стандартных структур тестирования, которые можно было бы встраивать в систему на кристалле. Такие структуры должны обеспечивать тестирование отдельных ядер и связей между ними. Рабочая группа P1500 предложила структуры, очень близкие к структурам граничного сканирования в стандарте 1149.1. Таким образом, освоение технологии граничного сканирования позволит разработчикам быть на уровне современных требований и тенденций при отладке, изготовлении, тестировании, внутрисхемном программировании и эксплуатации различных систем, а также поможет быстрее освоить множество новых высоких технологий в современной электронике. Литература

|

|

|

|

|

PDFs | Новости | Литература | Схемы | Форум | Блоги | Реклама |

╚Разделяй и властвуй╩ - принцип граничного сканирования.

╚Разделяй и властвуй╩ - принцип граничного сканирования.