|

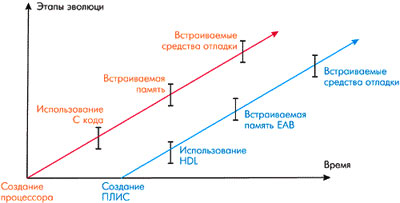

С. Хуторной Система Excalibur - средство разработки SoC-решений фирмы ALTERA. Часть 1. Общее описание системыПакет Excalibur, предлагаемый фирмой Altera, позволяет создавать программное и аппаратное обеспечение для SoC (system-on-chip) решений. SoC, построенная при помощи Excalibur, объединяет в одном кристалле процессор и периферию, необходимую для обработки различного рода информации (память, устройства ввода/вывода, различного рода интерфейсы и т.п.). В отличие от серийно выпускаемых микроконтроллеров, УСТРОЙСТВа НА БАЗЕ SoC Excalibur могут перестраиваться как аппаратно, так и программно при помощи стандартных средств пакета. В цикле будут представлены характеристики встраиваемого конфигурируемого процессора Nios, средств разработки аппаратного и программного обеспечения на базе системы Quartus и компилятора GNUPro. В первой части цикла будет рассмотрена структура ПЛИС APEX20K как платформы для создания SoC и краткое описание характеристик встраиваемого процессора Nios и САПР Quartus. Бурное развитие компьютерных технологий привело к тому, что цифровые системы стали внедряться в различные области человеческой деятельности. Это и обработка потоков данных в системах управления, и цифровая обработка сигналов (ЦОС), и системы сбора данных. Основой цифровой системы, как правило, является микропроцессор. Это может быть либо универсальный процессор, либо цифровой сигнальный процессор ЦСП (Digital Signal Processor - DSP). Очень часто в единой системе объединяются устройства с различными требованиями по производительности и параллелизму обработки данных. Если в процессе работы системы возникает необходимость в параллельных операциях с большой скоростью поступления данных, к примеру, многоканальная обработка сигнала в корреляторе навигационного при╦мника, или необходимость реализовать интерфейс микропроцессора с периферией, то разработчик вынужден использовать устройства так называемой "предпроцессорной" обработки. Роль таких "предпроцессоров" могут выполнять специализированные интегральные микросхемы (Appli-cation Specific Integrated Circuit - ASIC) или устройства на ж╦сткой логике, как правило, реализуемые на ПЛИС (программируемые логические интегральные схемы), которые имеют высокие характеристики по скорости и способны параллельно обрабатывать несколько массивов (каналов) информации одновременно. Система в итоге "распадается" на две части - программную (даже программно-аппаратную), реализуемую на серийно выпускаемых микропроцессорах, и аппаратную, построенную на ж╦сткой логике (ASIC, ПЛИС). Обе части системы требуют различного подхода к проектированию и различного рода навыков: с одной стороны, программиста ЦСП, а с другой - специалиста в области цифровой схемотехники. Разработчика цифровых систем, в первую очередь, интересуют два аспекта: производительность элементной базы и наличие отладочных средств. Главное преимущество системы, построенной на микропроцессорах, в частности, на ЦСП, - е╦ гибкость, то есть возможность на этапе разработки и тестирования реализовывать различного рода алгоритмы без изменений аппаратной части системы. Кроме того, фирмы-производители микропроцессорной техники осуществляют мощную информационную поддержку своих продуктов. Идея интеграции устройств различного назначения в единой системе привела к появлению микроконтроллеров. В отличие от его старшего брата микропроцессора, серийно выпускаемые микроконтроллеры обладают большим набором периферийных устройств. Это могут быть дополнительные блоки памяти, блоки интерфейсов различного назначения, встроенные АЦП и ЦАП, иначе говоря, вся необходимая и, что немаловажно, стандартная периферия, которая для микропроцессоров выполняется в виде внешних модулей. В микроконтроллере вся она или, по крайней мере, большая е╦ часть, выполнена в одном кристалле. По своей гибкости такие системы не уступают системам, построенным на микропроцессорах, тем более, что сердцем всей системы является вс╦ тот же микропроцессор. К примеру, ядром микроконтроллера MSP430 фирмы Texas Instruments является 16-разрядный RISC-процессор. В состав MSP430 входит ОЗУ (256 или 512 байт), ПЗУ (8 или 16 Кбайт), 14-разрядный АЦП, на входе которого стоит мультиплексор, набор из нескольких универсальных таймеров, встроенный аппаратный контроллер ЖКИ и так далее - то есть полный набор необходимого стандартного оборудования. Однако, несмотря на широкий выбор периферийных устройств, предлагаемых фирмами-производителями микроконтроллеров, вся периферия имеет ж╦сткую структуру. Таким образом, микроконтроллер со всей его оснасткой и серийный микропроцессор - это устройства, имеющие ж╦сткую структуру, и изменить конфигурацию какого-либо блока нельзя. Поэтому, если в проектируемой системе необходимо наличие каких-нибудь нестандартных устройств обработки, то вопрос о применении ASIC или ПЛИС оста╦тся открытым. Поэтому на рынке электронных компонентов можно найти различные специализированные микроконтроллеры или микросхемы, имеющие в сво╦м составе как необходимую логику, так и встроенные процессорные системы. По специфике деятельности автору статьи приходится сталкиваться с различного рода информацией о выпускаемых электронных системах, используемых при обработке сигналов навигационных спутников систем GPS/GLONASS. Примерами могут быть серийно выпускаемые кристаллы GP4020 (фирма MITEL), сходные по своей структуре со стандартными микроконтроллерами. В состав кристалла GP4020 входит набор устройств, которые можно условно разделить на две группы. К первой относится стандартный набор, содержащийся в любом микроконтроллере - это микропроцессорное ядро ARM7TDMI, 8-бит порт общего назначения с возможностью передачи данных по каждой линии отдельно, загрузочный сектор памяти ╦мкостью 512 байт, встроенная память RAM 8 Кбайт и порт RS232. Ко второй группе относятся устройства, используемые для решения специализированных задач - это 12 независимых корреляционных каналов со своей логикой управления. Дальнейшим развитием идеи интеграции различных устройств в одной системе стало понятие "система на кристалле" SoC (system-on-chip). Идея SoC - объединить в одном кристалле как можно большее количество элементов цифровой системы. В итоге, такие системы приобретут характеристики, присущие как микроконтроллерам, так и процессорам. Они становятся оптимизированными по размерам, потребляемой мощности, внутрисистемным задержкам распространения сигналов и команд и по электромагнитной совместимости внутри системы. Увеличение логической ╦мкости ПЛИС привело к тому, что они становятся полноправными конкурентам при реализации SoC. В такой реализации система на кристалле получила аббревиатуру SoPC (System on a programmable chip). Эволюция развития программируемых интегральных схем своими этапами напоминает развитие процессорной техники (рис. 1). Так же, как и процессор, ПЛИС прошла в сво╦м развитии этап создания языков высокого уровня для описания работы цифровых схем (VHDL, Verilog и т.п.), этап появления встраиваемых блоков памяти (Embedded Array Block) и наконец, появление встроенных систем отладки цифровых схем (SignalTap в кристаллах Altera). Поэтому не удивительно, что идея создания систем на кристалле постепенно перешла в идею создания систем в программируемом кристалле ПЛИС. Рисунок 1. Этапы эволюции процессора и ПЛИС

Основная идея создания SoPC состоит в том, чтобы дать разработчику полный набор стандартных средств, имеющихся у ЦСП и микроконтроллеров, плюс дополнительный объ╦м кристалла и необходимый сервис для реализации своих схемных решений. Таким образом, система приобрела не только программную гибкость, но и аппаратную, то есть теперь она не привязана к конкретной аппаратной архитектуре. Разработчик имеет широкие возможности для изменения не только программного обеспечения, но и большинства аппаратных блоков системы, включая микропроцессор. Ведущим мировым производителем ПЛИС является фирма Altera. Емкость кристаллов, производимых этой фирмой, достигла нескольких миллионов логических вентилей, а объ╦м встраиваемой памяти уже давно переш╦л стотысячный предел в битах. В качестве платформы для SoPC-решений фирма Altera предлагает использовать появившееся в 1999 году семейство ПЛИС APEX20К. Как возможный вариант этого решения, Altera предлагает систему Excalibur. Функционально весь пакет предлагаемой системы можно разбить на две части. Первая - собственно сама SoPC. В не╦ входит САПР Quartus - система 4-го поколения, появившаяся на рынке в 1999 году (отдельный CD, САПР полностью независима и может использоваться в других, не связанных с SoPC проектах), и дополнительное программное обеспечение для встраиваемого RISC-процессора Nios. Программное обеспечение поставляется на двух компакт-дисках: первый содержит компилятор/отладчик GNUPro фирмы RedHat с библиотекой программ, второй - программное обеспечение к пакету Quartus в виде дополнительной параметризируемой мегафункции встраиваемого процессора Nios. Вторая часть системы Excalibur - рабочее место разработчика (Development Board), позволяющее отладить программное и аппаратное обеспечение, не привязываясь к конкретному проекту. Благодаря своей программной и аппаратной гибкости, SoPC Excalibur может использоваться в качестве ядра во встраиваемых системах различного назначения. Это может быть компьютерная периферия, процессоры обработки изображения, системы промышленной автоматики, коммуникационное оборудование и т.п. Ядром всей системы является встраиваемый RISC-процессор Nios. Это первый 16- или 32-разрядный RISC-процессор, архитектура которого оптимизирована для SoPC-решения на базе кристаллов ПЛИС APEX. Компоненты SoPC Excalibur разрабатываются отдельно и хранятся в виде файлов параметризируемых программных модулей (мегафункций) для САПР Quartus, входящих в состав библиотеки компонентов проекта. Затем они объединяются в единый проект. Процессор Nios представлен в виде отдельного параметризируемого программного модуля. Все части проекта, как правило, стандартизованы, что позволяет использовать компоненты системы различных производителей (разработчиков). Фирма Altera предлагает большой выбор различного рода мегафункций: интерфейсные модули для шины PCI, универсальные асинхронные при╦мопередатчики (UART), модуль быстрого преобразования Фурье [3] и так далее. Любая из этих мегафункций может быть включена в проект как отдельный модуль и сконфигурирована под нужды разработчика. Для поддержки разработки встраиваемых систем на базе процессора Nios фирма Altera предлагает в качестве стенда плату или рабочее место разработчика. Плата включает в себя необходимый набор дополнительных аппаратных средств, помогающих отрабатывать взаимодействие системы с различными внешними устройствами. На плате расположены: кристалл APEX EP20K200E; FLASH-память ╦мкостью 1 Мбайт (512К╢16 бит); SRAM-память 256 Кбайт (2 кристалла по 64К╢16 бит); встроенная в плату логика на кристалле ПЛИС MAX7000 EPM7064AE, которая выполняет функции контроллера прошивки APEX из памяти FLASH. В табл. 1 представлено распределение FLASH-памяти [1]. Таблица 1. Распределение FLASH-памяти (1 Мбайт)

Плата также содержит разъ╦м для дополнительного модуля памяти SDRAM и два мезонинных разъ╦ма для PCI. Пользователю предоставлены завед╦нные на выводы кристалла ПЛИС, кнопочные переключатели, линейка дип-переключателей, светодиоды и жидкокристаллический двухрядный индикатор, большой набор штыревых разъ╦мов. В комплект поставки входит блок питания, комплект кабелей для LPT и COM портов, программатор ByteBlasterMV. Прошивка ПЛИС APEX может производиться либо по кабелю ByteBlasterMV, либо через встроенный контроллер из FLASH. Как было сказано выше, в качестве платформы для SoC-решений фирма Altera предлагает использовать появившееся в 1999 году семейство ПЛИС APEX20К. Поэтому, прежде чем приступить к описанию системы Excalibur, необходимо рассмотреть основные характеристики и структуру предлагаемых кристаллов. ПЛИС семейства APEX20KВ номенклатуре семейства APEX представлены кристаллы различной степени интеграции. В табл. 2 приведены характеристики кристаллов данного семейства [2]. Таблица 2. Характеристики кристаллов ПЛИС семейства APEX20K

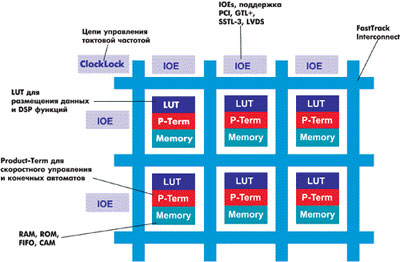

Кристаллы APEX объединяют в себе две разные архитектуры ПЛИС - вентильную и матричную. К матричным кристаллам ПЛИС относятся семейства: Classic, MAX3000, MAX5000, MAX7000 и MAX9000. К вентильным - FLEX6000, FLEX8000 и FLEX10K. Вентильные ПЛИС используют таблицы перекодировки (LUT - look-up-table). Матричные - матрицы распределения термов (product-term blocks). Каждая архитектура наилучшим образом подходит для реализации определ╦нных логических функций. Помимо этого, подобно микросхемам семейства FLEX 10K, в APEX имеется возможность реализации встроенной памяти RAM, ROM и FIFO (в том числе, двухпортовой). В отличие от кристаллов FLEX10K, память APEX расположена в специальных встраиваемых системных блоках ESB (Embedded System Block). Все три элемента (product-term blocks, look-up-table и ESB) составляют основу MultiCoreTM архитектуры (рис. 2). Рисунок 2. ПЛИС APEX, MultiCoreTM архитектура

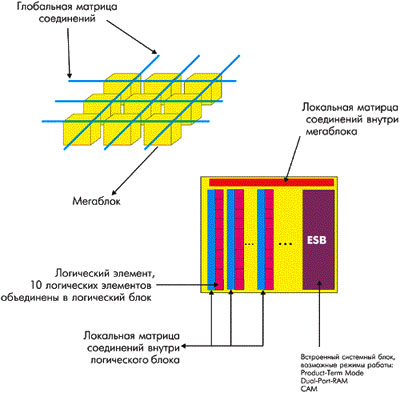

Верхним уровнем иерархической структуры кристалла является мегаблок (MegaLAB), состоящий из логических блоков и элементов (блоков) памяти ESB. На рис. 3 изображена структура мегаблока со встроенным блоком памяти и глобальной матрицей соединений. Построение системы на основе мегаблоков имеет ряд существенных преимуществ. Подобная организация соединений позволяет выделять дополнительные ресурсы при трассировке кристалла. В мегаблоке может разместиться законченный фрагмент системы. Рисунок 3. Структура мегаблока со встроенной матрицей соединений

Каждый мегаблок состоит из 16 (для кристаллов APEX20K60┘20K600) или 24 (для кристаллов APEX20K1000┘20K1500) логических блоков. Логический блок содержит структуры, называемые логическими элементами LE (logic element). В каждом логическом блоке содержится по десять LE. Взаимодействие между ними внутри логического блока происходит при помощи глобальной матрицы соединений, которая имеет непрерывную структуру (FastTrack Interconnect routing structure) и разделена на строки и столбцы. Особенностью архитектуры является то, что каждый логический элемент в блоке может соединяться при помощи глобальной матрицы соединений не только с элементами внутри блока, но и с логическими элементами соседнего логического блока. Благодаря этому, расширяются возможности по трассировке ПЛИС. Логические элементы - основа построения большинства цифровых устройств на кристаллах ПЛИС. Каждый из них состоит из: четыр╦хвходовой таблицы перекодировок (LUT), упомянутой ранее; цепей каскадирования (cascade-out) и ускоренного переноса (Carry-in, Carry-out); универсального триггера с управляющей логикой. Четыр╦хвходовая таблица перекодировок - это что-то вроде функционального генератора, который может быстро реализовать любую логическую функцию четыр╦х переменных. Каждый логический элемент, помимо внутренних соединений, подключен к локальной матрице соединений внутри логического блока. Также он имеет выход на матрицу соединений в структуре мега-блока и на глобальную матрицу соединений (FastTrack Interconnect routing structure). Два независимых выхода LE могут управляться таблицей перекодировок или выходом триггера, каждый из этих выходов может управлять структурой, подключенной как к локальной матрице соединений мегаблока, так и к глобальной матрице соединений всей ПЛИС. Архитектура кристалла APEX обеспечивает два типа специализированных высокоскоростных тракта прохождения данных, которые соединяют смежные логические элементы: cascade chains и carry chains. Тракт каскадирования (cascade chains) используется в логических операциях, к примеру, в компараторе с минимальным временем отклика. Для реализации быстрого переноса в арифметических операциях используется тракт прохождения carry chains. Логические элементы могут работать в различных режимах. Основным режимом является нормальный (normal mode), он оптимален при реализации логических функций: комбинаторной логики и функций декодирования. При этом основная нагрузка ложится на таблицы перекодировок и цепи синхронизации. Арифметический режим работы логического элемента (arithmetic mode), исходя из названия, лучше всего подходит для реализации на кристалле арифметических функций. Третий по значению - это режим сч╦тчика (counter mode). В этом режиме к работе подключается универсальный триггер со своей схемой управления. В зависимости от реализуемой схемы, трассировщик Quartus включает логический элемент в соответствующий режим работы, активизируя ту или иную его часть. Если в процессе проектирования наблюдается нехватка логических ресурсов кристалла при избытке ресурсов памяти, то встраиваемые системные блоки (ESB) могут работать не только как блоки памяти. На стадии компиляции и трассировки часть логических функций переносится в ESB, при этом он переключается в режим матрицы распределения термов. В этом режиме один блок ESB разбивается на 16 макроячеек (macrocell). Структура макроячейки аналогична структуре таковой в кристаллах MAX3000 и MAX7000. В е╦ состав входят: программируемая матрица, параллельный расширитель и программируемый универсальный триггер. Каждая макроячейка может быть сконфигурирована индивидуально. При реализации комбинаторной логики используется программируемая матрица и параллельный расширитель. Для регистровых функций используется программируемый триггер, который может быть настроен на работу в режиме D-, T-, JK- или SR-триггера. При использовании ESB в качестве блока памяти, помимо стандартных элементов, реализуемых на кристаллах FLEX10K, кристаллы APEX позволяют включать элементы памяти, адресуемой по содержимому (CAM - Content-addressable memory). Преимущество CAM заключается в малом времени доступа. В табл. 3 представлены характеристики элементов памяти, встраиваемых в кристалл APEX, и необходимое для их реализации количество блоков ESB. Таблица 3. Поддержка модулей памяти в кристаллах APEX20K

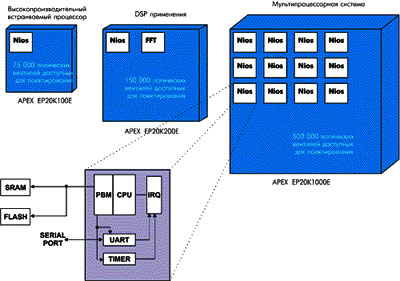

ПЛИС семейства APEX имеют необходимые средства по управлению тактовыми сигналами: ClockLock - уменьшение задержки тактового сигнала; ClockBoost - умножение частоты; ClockShift - программируемый фазовый сдвиг. Все функции управления тактовой частотой кристалла реализованы в виде параметризируемой мегафункции. Управляя параметрами этой мегафункции, можно добиться умножения частоты входного тактового сигнала и запрограммировать несколько входов тактовой частоты со своими фазовыми сдвигами относительно глобального тактового сигнала. Система ClockLock позволяет уменьшить временные запаздывания различных частей схемы относительно глобального тактового сигнала. Для взаимодействия ПЛИС с внешним миром в архитектуре кристаллов APEX предусмотрена возможность работы с внешними сигналами различного уровня. Аналогично кристаллам FLEX10K, кристаллы APEX поддерживают спецификацию уровней шины PCI. Расширены возможности совместимости по выходам с такими стандартами, как LVCMOS (low voltage complementary metal-oxide semiconductor), LVTTL (low voltage transistor-to-transistor logic), AGP (advanced graphics port) и HSTL (high speed transceiver logic). Микросхемы семейства APEX20K изготавливаются по технологии статического ОЗУ (SRAM). Загрузка конфигурации может быть произведена различными способами. При включении питания конфигурация в ПЛИС может быть загружена при помощи последовательного ПЗУ. Фирма Altera предлагает набор необходимых микросхем ПЗУ. При наличии на плате необходимой логики управления конфигурация ПЛИС может быть загружена из внешней FLASH-памяти либо из файла конфигурации. Altera поставляет стандартные средства программирования/конфигурации, такие как кабели связи ByteBlasterMV или Master-Blaster. Они позволяют программировать ПЛИС непосредственно из последовательного или параллельного порта компьютера по последовательному интерфейсу JTAG [4]. Общее описание встраиваемого процессора NiosЯдро всей системы Excalibur - процессор Nios. Это первый RISC-процессор, архитектура которого оптимизирована под SoPC-решения на базе ПЛИС. Средства конфигурации позволяют оптимальным образом выбрать характеристики встраиваемого процессора именно для данного приложения. Широкие пределы оптимизации способствуют использованию Nios в приложениях различной степени сложности: от высокопроизводительных встраиваемых приложений до создания мультипроцессорных систем. В табл. 4 даны краткие характеристики процессора с 16- и 32-бит архитектурами. Число используемых логических элементов кристалла ПЛИС зависит от структуры выбранного процессора - это может быть 16- или 32-бит приложение. Но и в пределах одной структуры это число может существенно изменяться. Так, к примеру, при прошивке 32-разрядного процессора в ПЛИС EP20K200E в кристалле оста╦тся порядка 80% свободного пространства. Таблица 4. Архитектура процессора Nios

Процессор имеет конвейерную архитектуру, позволяющую выполнять одну 16-бит инструкцию за один такт. Система команд Nios приспособлена к служебным программам, составленным на языках высокого уровня C и C++. Она включает стандартный набор арифметических и логических операций, команды поддерживают поразрядные и побайтовые операции. Процессор имеет большой набор регистров общего назначения. Их разрядность может изменяться, в зависимости от конфигурации процессора - 16- или 32-разрядные. Число регистров тоже может изменяться в процессе конфигурации от 64 до 512. Программы могут обращаться к любому из них при помощи скользящего окна длиной в 32 регистра. Скользящее окно перекрывает весь набор доступных программисту регистров. На рис. 4 показана структурная схема процессора. Процессор поддерживает широкий набор периферийных устройств. Сюда входят таймер/сч╦тчик, последовательный порт, порты ввода/вывода различного назначения, IDE-контроллер, 10/100 Ethernet MAC и SDRAM- контроллер [5]. Помимо этого, фирмой Altera предлагаются ядра (core) так называемой интеллектуальной собственности, которые могут быть использованы как независимые части общего проекта. Каждое из них можно изменять по своему усмотрению, меняя характеристики и количество. В Nios предусмотрена поддержка внешней и встроенной памяти. 5-ступенчатая конвейерная архитектура позволяет выполнять одну инструкцию за один цикл процессора. Процессор поддерживает различные режимы адресации, до 64-х векторных прерываний. Наряду с построением систем с одним процессором, программно/аппаратная гибкость Nios позволяет использовать его как основу для модульного наращивания системы в рамках одной унифицированной архитектуры (рис. 4). Рисунок 4. Структура процессора Nios

Краткие характеристики САПР QuartusДля проведения всех необходимых изменений в конфигурации процессора, разработки дополнительной логики и проведения функционального и временного моделирования отдельных частей проекта используется система автоматизированного проектирования Quartus [6]. Появление системы связано с выходом на рынок новых кристаллов ПЛИС APEX. Так же, как и предыдущая версия САПР MAX+PLUS II, система Quartus поддерживает разнообразные средства описания проекта: схемный ввод, описания проекта языками VHDL или Verilog. В дополнение к этому, введ╦н редактор блоков (Block Editor), графическое средство описания параметризируемых модулей. FloorPlan Editor или поуровневый планировщик может распределять ресурсы кристалла как на уровне мегаблоков, так и на более низком уровне - логических блоков. Улучшены сервисные функции по ориентации в иерархической структуре проекта, для этого введено новое средство - Project Navigator. Система Quartus предоставляет разработчику широкие возможности по различным изменениям при компиляции проекта. Дело в том, что при разработке проекта, включающего большое количество разнообразных блоков и функциональных модулей, проектировщик со временем сталкивается с проблемой, когда компиляция проекта занимает большое количество времени. Если изменения при очередной итерации проекта затронули не весь проект, а его небольшую часть, то в системе имеется возможность так называемой nSTEP-компиляции. При этом процесс компиляции затрагивает лишь те части проекта, которые были изменены. Это не только сокращает сроки разработки системы, но и сохраняет на кристалле прежние временные характеристики остальной части схемы. При компиляции проекта производится анализ всех его функциональных блоков на предмет реализации их в соответствующих структурах кристалла (LUT, матрице распределения термов, блоках памяти), чем достигается высокая эффективность размещения на кристалле, приводящая к высокой производительности конечного изделия. Процесс такого размещения называется CoreSyn Synthesis. Так же, как и в системе MAX+PLUS II, в пакете Quartus есть возможность временного и функционального анализа схемы. Помимо этого, в Quartus включено новое средство тестирования системы в реальном режиме времени - Signal-Tap [7]. Это не что иное, как параметризованная мегафункция, входящая в стандартный комплект поставки. Эта функция позволяет в процессе работы самого кристалла контролировать состояние внутренних точек проекта, заданных пользователем. В процессе работы мегафункция переводит данные во встроенные блоки памяти кристалла (ESB), которые затем поступают в компьютер через коммуникационный кабель MasterBlaster и выводятся на экран в редакторе временных диаграмм (Waveform Editor) для просмотра, анализа и отладки схемы. MasterBlaster обеспечивает аппаратный интерфейс между микросхемами APEX и компьютером, выполняет загрузку и анализ ПЛИС через шину USB со скоростью до 8 Мбит/с или последовательный порт RS-232 со скоростью до 115000 бит/с. Анализатор SignalTap может работать также и через ByteBlasterMV. Что дальше?В следующей статье этого цикла предполагается предложить Вашему вниманию более подробное описание встраиваемого процессора Nios и средств разработки программного и аппаратного обеспечения для него на базе компиляторов GNUPro и САПР Quartus, соответственно. Литература:

|

|

|

|

|

PDFs | Новости | Литература | Схемы | Форум | Блоги | Реклама |

Система Excalibur - средство разработки SoC-решений фирмы ALTERA. Часть 1. Общее описание системы.

Система Excalibur - средство разработки SoC-решений фирмы ALTERA. Часть 1. Общее описание системы.