|

М. Кузелин ПЛИС фирмы Xilinx с архитектурой FPGA: семейство Spartan-IIEВ ноябре 2001 года компания Xilinx объявила о начале выпуска нового семейства ПЛИС с архитектурой FPGA - семейства SpartanTM-IIE (напряжение питания ядра кристалла - 1,8 В). Семейство SpartanTM-IIE - четв╦ртое поколение ПЛИС серии Spartan, призванной заменить в крупносерийных изделиях заказные микросхемы. Основными особенностями, позволяющими ПЛИС серии Spartan конкурировать с заказными микросхемами, являются: сопоставимая цена, значительно меньшее время разработки проекта пользователя, возможность корректировки ошибок или внесения изменений в конфигурацию микросхемы непосредственно в готовом устройстве. ПЛИС семейства Spartan-IIE могут применяться в системах с тактовыми частотами до 200 МГц, поддерживают 19 стандартов ввода/вывода, среди которых 3 дифференциальных стандарта (LVDS, BLVDS и LVPECL), содержат 4 модуля управления синхронизацией. Семейство содержит 5 микросхем, отличающихся логической ╦мкостью, в свою очередь, каждая микросхема выпускается в нескольких корпусах. Основные параметры микросхем семейства Spartan-IIE представлены в табл. 1. Таблица 1. Основные параметры микросхем семейства Spartan-IIE

Кристаллы семейства Spartan-IIE производятся на основе статического ОЗУ (Static Random Access Memory - SRAM), поэтому функционирование кристаллов определяется загружаемыми во внутренние ячейки памяти конфигурационными данными. Конфигурационные данные могут загружаться в кристалл несколькими способами. В ведущем последовательном режиме (Master Serial) загрузка осуществляется из внешнего ПЗУ и полностью управляется самой FPGA Spartan-IIE. В других режимах управление загрузкой осуществляется внешними устройствами (подчин╦нный параллельный режим Slave Parallel, подчин╦нный последовательный Slave Serial и JTAG). Для хранения конфигурационной последовательности компанией Xilinx выпускаются однократно программируемые последовательные ПЗУ серии XC17S00A и многократно перепрограммируемые непосредственно в устройстве параллельные/последовательные ПЗУ серии XC18V00. Конфигурационные данные создаются пользователем при помощи программного обеспечения проектирования ISE, бесплатная версия которого (ISE Web-Pack) доступна для загрузки по адресу http://www.xilinx.com/sxpresso/webpack.htm. Программное обеспечение включает в себя модули схемного и текстового ввода, моделирования, автоматического и ручного (только в платной версии) размещения и трассировки, создания, загрузки и верификации конфигурационных данных. Архитектура кристалла семейства Spartan-IIE основана на архитектуре семейства Virtex-E и состоит из пяти основных конфигурируемых элементов:

Отличие архитектуры семейства Spartan-IIE от архитектуры семейства Virtex-E заключается в меньшем в 2 раза количестве блоков памяти и блоков управления синхронизацией. Блок-схема архитектуры семейства Spartan-IIE показана на рис. 1. Рисунок 1. Обобщ╦нная блок-схема ПЛИС семейства "Spartan-IIE"

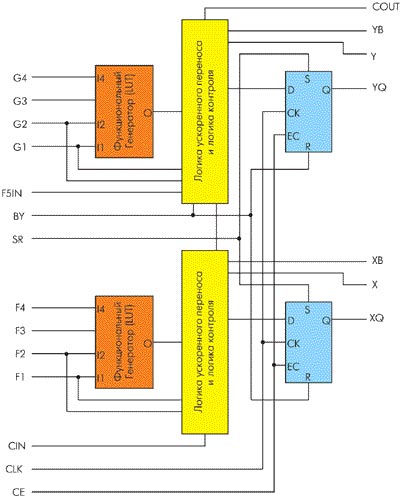

Конфигурируемый логический блок (КЛБ)КЛБ состоит из двух секций, каждая из которых состоит из двух 4-входовых функциональных генераторов, логики ускоренного переноса и двух регистровых элементов (рис. 2). Каждый КЛБ содержит два буфера с тремя состояниями, которые позволяют реализовать внутрикристальные шины. Аналогичные ПЛИС других фирм таких буферов не имеют, а эмулируют их за сч╦т использования функциональных генераторов. Рисунок 2. Структура КЛБ

Функциональные генераторы реализованы в виде 4-входовых таблиц преобразования (Look-Up Table - LUT). Кроме использования в качестве функциональных генераторов, каждый LUT-элемент может быть также использован как синхронная память типа RAM размерностью 16x1 бит. Более того, из двух LUT-элементов в рамках одной секции можно реализовать синхронную RAM-память размерностью 16x2 или 32x1 бит, либо двухпортовую синхронную RAM-память размерностью 16x1 бит. На LUT-элементе микросхемы Spartan-IIE может быть реализован 16-бит сдвиговый регистр, который идеально подходит для захвата высокоскоростных или пакетных потоков данных. Этот режим может также использоваться для запоминания данных в приложениях цифровой обработки сигналов. Блоки ввода/выводаБлоки ввода/вывода поддерживают 19 сигнальных стандартов ввода/вывода, включая дифференциальные стандарты LVDS, BLVDS и LVPECL. Дифференциальные стандарты LVDS и BLVDS позволяют коммутировать ПЛИС семейства Spartan-IIE с другими микросхемами на плате без использования дополнительных конверторов или трансляторов. Помимо этого, дифференциальные стандарты более скоростные, чем однопроводные, позволяют снизить энергопотребление кристалла и шумы, а также устраняют электромагнитные наводки. В табл. 2 представлены все поддерживаемые стандарты ввода/вывода. Совместимость по входу с 5-В логическими сигналами обеспечивается подключением последовательного резистора на 100 Ом. Таблица 2. Поддерживаемые Spartan-IIE стандарты ввода/вывода

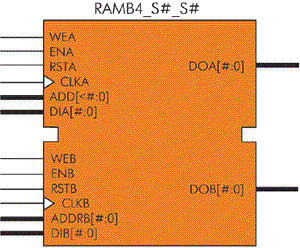

Блочная память (Block RAM)Каждый блок памяти (рис. 3) - это синхронная двухпортовая RAM с независимым управлением для каждого порта. Размерность шины данных для обеих портов может быть сконфигурирована независимо, что позволяет создавать преобразователи размерности шины. В табл. 3 показаны возможные соотношения размерностей шин данных и адреса. Таблица 3. Возможные соотношения размерностей шин данных и адреса

Рисунок 3. Блочная память

Модули автоподстройки задержки (DLL)Полностью цифровая автоподстройка задержки (DLL) может устранять перекос задержек между синхросигналом на входном контакте микросхемы и сигналами на тактовых входах внутренних схем устройства. Дополнительная задержка вводится таким образом, чтобы фронты сигналов синхронизации достигали внутренних триггеров в точности на один период синхронизации позже их прихода на входной контакт. Эта система с обратной связью эффективно устраняет задержку распределения сигналов синхронизации, гарантируя, что фронты синхросигналов на входе микросхемы и на внутренних тактовых входах с большой точностью синхронны. Вдобавок, для устранения задержек, возникающих при распределении тактовых сигналов, DLL созда╦т новые возможности управления функциями синхронизации. Модуль DLL может создавать четыре квадратурные фазы из исходного источника синхросигнала; удваивать частоту синхросигнала или делить эту частоту на 1,5, 2, 2,5, 3, 4, 5, 8 или 16. Модуль DLL также функционирует как тактовое зеркало. Пут╦м вывода из микросхемы сигнала с выхода DLL и последующего ввода этого сигнала снова внутрь кристалла, схема DLL может устранить разбег фаз для тактовых сигналов на уровне печатной платы при работе с несколькими микросхемами Spartan-IIE. Чтобы гарантировать, что системная синхронизация будет нормально функционировать до момента окончания конфигурирования системы и начала штатной работы, схема DLL имеет возможность задерживать процесс конфигурирования до нормальной синхронизации с системой. В настоящее время выпускаются микросхемы XC2S50E, XC2S100E, XC2S200E и XC2S300E, выпуск микросхемы XC2S150E планируется начать во II квартале 2002 года. Микросхемы XC2S50E и XC2S300E поступили на склад дистрибьютора Xilinx в Москве в декабре 2001 года. Подробная информация о семействе представлена на web-сайте компании Xilinx: www.xilinx.com. Литература

|

ПЛИС фирмы Xilinx с архитектурой FPGA: семейство Spartan-IIE

ПЛИС фирмы Xilinx с архитектурой FPGA: семейство Spartan-IIE