|

Т. Солохина, Я. Петричкович, А. Глушков, А. Беляев, Ю. Грибов, В. Никольский, В. Силин, М. Алексеев, Ю. Александров

Время кентавров: Микросхемы серии Мультикор-11xx (MC-11xx) для встраиваемых и мобильных применений

"Кентавры - дикие существа, полулюди-полукони, обитатели гор и лесных чащ, отличаются буйным нравом и невоздержанностью, однако никогда никому не причиняют вреда сознательно". По мнению Я. Петричковича, Главного конструктора проекта, идея двухпроцессорных Мультикоров такова. RISC-ядро - это интеллектуальная (человеческая) голова Кентавра. Она (голова) управляет вычислительным процессом, который реализует чип Мультикор. DSP-ядро в чипе - это лошадиные ноги кентавра. Это то, что нес╦т на себе смысловую нагрузку ускорителя-акселератора (для головы или RISC-ядра), позволяя Кентавру быстро бегать. В результате такой комбинации (RISC-ядро + DSP-ядро) получается этакое суперсущество, умеющее одновременно и интеллектуально мыслить и быстро бегать.

Таблица 1. Сравнение DSP-ядра (ELCORE-11) и DSP-ядра семейства TMS320C54x, использованного в новой двухпроцессорной микросхеме TMS320C5471 (TI)

|

DSP-ядро

|

TMS320C54x

|

|

1

|

Программный конвейер - 3 фазы

|

Программный конвейер - 6 фаз. Это усложняет программирование

|

|

2

|

Параллельно выполняется до 3-х арифметических операций (умножение, сложение, вычитание)

|

Параллельно выполняется до 2-х арифметических операций (умножение и сложение при MAC либо два сложения)

|

|

3

|

32-разрядная операция сложения/вычитания выполняется за 1 такт

|

32-разрядная операция сложения/вычитания выполняется за 2 такта

|

|

4

|

Поддержка формата 32Е16 с плавающей точкой

|

Нет

|

|

5

|

Поддержка цикла DO, DOFOREVER. Допускается вложенность до 7 циклов

|

Циклы не поддерживаются. Имеются команды повтора RPT, RPTB, но они не допускают вложенности. Внутри повторяемых блоков не могут использоваться команды управления

|

|

6

|

Адресный генератор содержит в общей сложности 27 регистров, что обеспечивает большую гибкость при формировании адресов операндов

|

Адресный генератор содержит в общей сложности 10 регистров

|

Микросхемы серии Мультикор-11xx (MC-11xx) относятся к новому классу приборов - цифровых сигнальных контроллеров или DSC (Digital Signal Controller), которые объединяют в одном кристалле RISC-ядро и цифровой процессор обработки сигналов (DSP-ядро). Микросхемы серии МС-11 разрабатываются на базе процессорных ядер платформы проектирования "МУЛЬТИКОР" или "MULTICOR-E"TM.

Платформа "МУЛЬТИКОР" разработана в ГУП НПЦ ЭЛВИС и предназначена для проектирования широкого спектра сверхбольших интегральных микросхем (СБИС) для коммерческих, военных и космических применений, которые различаются по вычислительной мощности, стоимости и функциональным возможностям.

Платформа "МУЛЬТИКОР" по современной терминологии относится к классу ASPPs (Application Specific Prog-ram-mable Platforms) и представляет набор мощных современных аппаратно-программных средств проектирования СБИС и систем на их основе. Эти средства объединены общим маршрутом проектирования (6-9 месяцев), который обеспечивает сквозную верификацию разрабатываемых СБИС с использованием IP-ядер (IP-cores) из базы системы проектирования.

Для эффективной разработки приложений на базе платформы "МУЛЬТИКОР" разработано мощное инструментальное программное обеспечение (ПО), не уступающее по функциональным возможностям зарубежным аналогам (под операционные системы Windows и Linux).

Микросхемы серии МС-11 содержат стандартное RISC-ядро (RISCore-11TM) с системой команд MIPS 1 ISA® и оригинальное, масштабируемое и программируемое ядро цифрового сигнального процессора - DSP-ядро (DSP - Digital Signal Processing) ELCORETM (ELVEESs CORE).

В состав микросхем МС-11 включена минимальная конфигурация DSP-ядра - "ELCORE-11", имеющая 16-разрядную гарвардскую SISD-архитектуру (Single Instructions Single Data - один поток команд и один поток данных). По общей классификации СБИС, разрабатываемых на базе платформы "МУЛЬТИКОР", СБИС серии МС-11 относятся к сигнальным контроллерам мини-конфигурации.

Микросхема МС-11Т спроектирована на основе 0,54-мкм (3 металла) библиотеки российского изготовителя (ОАО "Ангстрем") и запущена в изготовление в конце II квартала 2002 года. Библиотеки макроблоков и в целом топология СБИС разработаны в ЗАО НЦ "Ангстрем-СБИС".

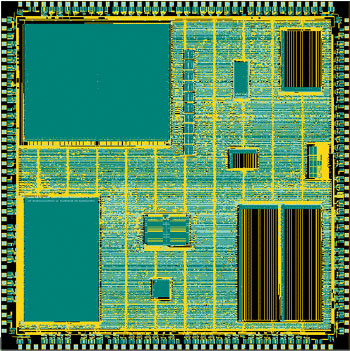

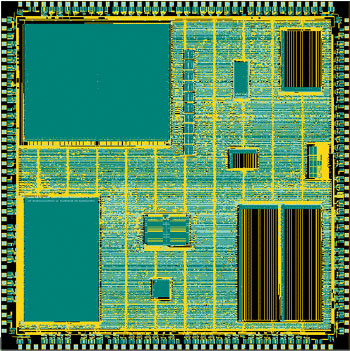

Микросхема МС-11Т имеет интеграцию около 2 млн. вентилей и размеры кристалла 10,1x10,1 мм (рис. 1). Опытные образцы ожидаются в IV квартале 2002 г.

Рисунок 1. Топология сигнального контроллера MC-11T

СБИС МС-11T может использоваться одинаково успешно для нескольких направлений применений, обеспечивая оптимальные показатели по весогабаритным параметрам и энергопотреблению:

- экономичных 16/32-разрядных микроконтроллеров для встраиваемых и мобильных применений;

- связных процессоров (однокристальных цифровых модемов) для мобильных и фиксированных применений;

- цифровых процессорных ядер для GPS/GLONASS при╦мников;

- цифровых процессорных ядер для программируемых аудиокодеров/декодеров нового поколения при объединении с аналоговыми ядрами ЦАП и так далее;

- цифровых ядер для микросхем цифрового телевидения и так далее;

- интеллектуальных терминалов доступа в Интернет, системы спутникового Интернета;

- интеллектуальных проводных и беспроводных охранных систем аудио- и видеонаблюдения;

- мультимедийных систем (игр, проигрывателей и так далее).

МС-11T сможет замещать ряд 16/32-разрядных серий приборов зарубежного производства, таких как микроконтроллеры / связные процессоры мировых лидеров TMS320 C54xx (TI), в частности, TMS 320C5471, DSP566хх/568xx, StarCore 110 (Motorola), микроконтроллеры для различных встраиваемых применений, для управления моторами ADSP218x/219x (Analog Device) и так далее.

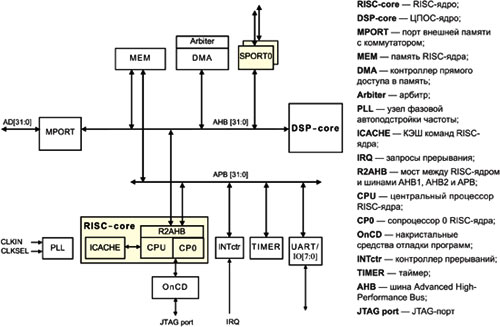

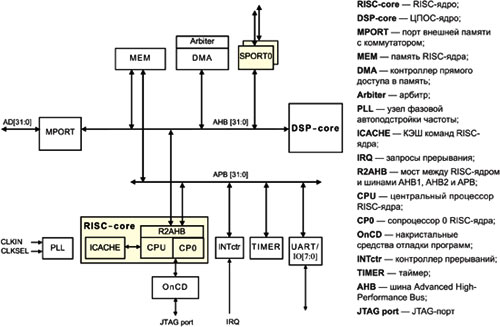

Структура микросхемы МС-11 приведена на рис. 2. Микросхема включает:

- процессорное RISC-ядро (RISC-core, RISCore-11);

- процессорное ЦПОС-ядро (DSP-core) с архитектурой SISD (Single Instruction Single Data) с возможностью обработки данных в форматах фиксированной и (программно) плавающей точки;

- ядро 8-канального контроллера DMA (Direct Memory Access);

- внутреннюю память:

- ОЗУ RISC-ядра объ╦мом не менее 8 Кбайт (MEM);

- КЭШ инструкций RISC-ядра (ICACHE)объ╦мом не менее 2 Кбайт;

- ОЗУ данных ЦПОС-ядра объ╦мом не менее 4 Кбайт;

- ОЗУ программ ЦПОС-ядра объ╦мом не менее 8 Кбайт;

- внешние интерфейсы:

- 32-разрядный порт памяти MPORT(Memory Port);

- средства отладки программ с интерфейсом JTAG OnCD (On Chip Debugger);

- UART;

- 2 последовательных порта (совместимых с портами SPORTS, ADI);

- ядро контроллера прерывания (INTctr - Interrupt controller);

- ядро 32-разрядного таймера (TIMER);

- ядро фазовой автоподстройки частоты (PLL).

Рисунок 2. Структура МС-11T

Рисунок 3. Корпус микросхемы MC-11T

RISC-ядро является ведущим в двухпроцессорной конфигурации и выполняет основную программу. Для RISC-ядра обеспечен доступ к следующим ресурсам DSP-ядра (DSP-core), являющегося ведомым по отношению к RISC-ядру: обмен данными RISC-ядра с ресурсами ЦПОС-ядра выполняется по командам LOAD, STORE. Память DSP-ядра и его регистры для RISC-ядра 32-разрядные (словные), то есть состояние двух младших разрядов адреса игнорируется.

RISC-ядро управляет работой ЦПОС-ядра посредством передачи ему задания (макрокоманды) с последующим запуском ЦПОС-ядра (перевод из режима STOP в режим RUN). С другой стороны, DSP-ядро формирует следующие прерывания в RISC-ядро:

- программное;

- по переполнению стека;

- при выполнении команды STOP;

- при достижении адреса останова при исполнении программы до адреса останова или завершении требуемого числа шагов при пошаговом исполнении программы.

DSP-ядро также обеспечивает вычисления в формате с плавающей точкой (врезка) высокой точности (32E16 или 16E16) c производительностью до 20 MFLOPs (для смеси умножений и сложений/вычитаний).

|

Подпрограмма вычислений с плавающей точкой

;MEMORY initialization

CLRL R28 0xFFFF,M5

MOVE 0,A5

MOVE 1<<30,R0.L ;+A=1

MOVE R0,(A5)+

MOVE 1,R0.L

MOVE R0,(A5)+ ;-

MOVE 1<<30,R0.L ;+d=2

MOVE R0,(A5)+

MOVE 2,R0.L

MOVE R0,(A5)+ ;-

MOVE 2,R0.L ;+N=2

MOVE R0,(A5)+ ;-

;AG initialization

INC R29,R29 1,A5

CLR R16

MOVE (A5+3),R2

LSL 8,R29,R3 CLRL R14 R29,I5

TR R2,R3 CLR R2 R3,PDNR

MSKG 1,R29 CLRL R0 (A5)-,R4

MSKG 3,R29 CLRL R0 R29,M5

DO R3,#Lp

CMPE R16,R4,R16 (A5)-I5,R4

ASRLE R17,R14,R4 INC R16,R16

ADCLs R4,R14,R14 R0,R10

CMPE R16,R2,R16

ASRLE R17,R14,R10 INC R16,R16

ADCLs R10,R14,R14 (A5)-I5,R4

CMPE R2,R4,R2 (A5)-I5,R4

ASRLE R3,R0,R4 INC R2,R2

Lp: ADCLs R4,R0,R0 (A5)-I5,R4

PDNLE R14,R16

ASLL R17,R14,R14 SUB R17,R16,R16

TR R28,R17 6,A5

INC R28,R2 R16,(A5)-I5

ASL 1,R2,R2

MOVE (A5-1),R4

TR R28,R5 DEC R4,R4 R14,(A5)

PDNLE R4,R2 R2,A5

ASLL R3,R4,R0 SUB R3,R29,R2 (A5)+I5,R4

MPSU R1,R4,R8 (A5)-I5,R6 ;

MPSU R5,R0,R10 ADD R6,R2,R2 (A5)-I5 ;Float pointB

MPSS R1,R5,R0 ADDLRTR R10,R8,R8 ;Multiplication

ADC16L R8,R0,R0 (A5)-I5,R6 ;

PDNLE R0,R2 (A5)-I5,R4 ;

ASLL R3,R0,R0 SUB R3,R2,R2 R29,M5 ;

CMPE R2,R6,R2 (A5)+ ;

ASRLE R3,R0,R4 INC R2,R2 (A5)+,R6 ~;Float point

TR R6,R4 ADCLS R4,R0,R0 R28,R5 ~;Add

PDNLE R4,R6 ;

ASLL R7,R4,R4 SUB R7,R29,R6 ;

MPSU R1,R4,R8 AD1 R6,R2,R2

MPSU R5,R0,R10

MPSS R1,R5,R0 ADDLRTR R10,R8,R8

ADC16L R8,R0,R0 (A5)+

PDNLE R0,R2 (A5)+

ASLL R3,R0,R0 SUB R3,R2,R2 R28,R3

MOVE R0,(A5)+

MOVE R2,(A5)

STOP

.end

|

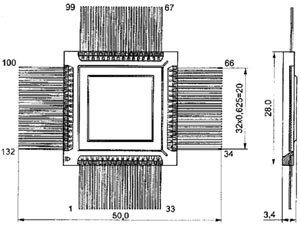

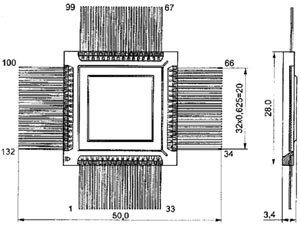

МС-11T размещается в 132-контакт-ном корпусе 4229.132 ("Монополия") и имеет следующие группы выводов:

- порт внешней памяти - 63;

- управление, включая, в том числе, JTAG диагностический порт - 17;

- 2 последовательных порта (SPORTS, ADI) - 12;

- UART - 8;

- электропитание - 32.

Назначение выводов МС-11T приведено в табл. 3-7.

Таблица 2. Основные технические характеристики сигнального микроконтроллера Мультикор-11T

|

Параметр

|

Значение параметра*

|

|

Технология изготовления

|

Заказная КМОП СБИС на библиотеке ОАО "Ангстрем", технологические нормы 0,54-мкм

|

|

Рабочая частота, МГц

|

50

|

Пропускная способность при нормальной температуре, МГц, не менее:

Порт памяти

Последовательные порты (SHARC)

|

50

25

|

|

Число каналов DMA

|

8

|

|

Разрядность программируемых таймеров

|

32 или 2 таймера по 16

|

|

Режимы энергосбережения

|

Несколько специальных архитектурных решений и режимов энергосбережения, обеспеченных для мобильных и бортовых применений МС-11.

Вход в режим программно, выход из режима по внешним прерываниям

|

|

Порт JTAG

|

Тестирование и отладка программ

|

|

Пиковая производительность при нормальной температуре, млн.оп./с

|

до 400 в 8-разрядном формате

до 150 в 16-разрядном формате

до 20 (программно) в формате 32E16

до 113 в 32-разрядном формате

|

|

Объ╦м внутреннего ОЗУ данных RISC-ядра*

|

не менее 8 Кбайт

|

|

Объ╦м кэш команд RISC-ядра

|

не менее 2 Кбайт

|

|

Объ╦м внутреннего ОЗУ данных DSP-ядра

|

не менее 4 Кбайт

|

|

Объ╦м внутреннего ОЗУ программ DSP-ядра

|

не менее 8 Кбайт

|

|

Порты

|

Порт UART.- Имеется режим использования его внешних контактов в качестве 8-разрядного поля флагов

Последовательные порты:

Порт памяти:- Поддержка статической памяти типа SRAM, FLASH, а также синхронной памяти типа SDRAM

- Программное задание циклов ожидания

- 4 внешних прерывания

- 4 внешних запроса DMA

|

|

Система инструкций

|

RISC-ядро и СБИС в целом ≈ MIPS-I ISA, включая аппаратно поддержанное умножение и деление; ядро DSP-ядра - полностью программируемое, поддержка коммуникационных и мультимедийных функций

|

|

Условия эксплуатации

|

-60 √ +125╟С

|

|

Корпус

|

132 вывода, металлокерамический - 4229.132

|

*) Для нормальной температуры. Параметры будут уточнены по результатам измерений. Внутренняя память МС-11 будет увеличена с переходом на улучшенную

технологию изготовления.

Таблица 3. Назначение выводов порта внешней памяти

|

Наименование сигнала

|

Количество

|

Тип

|

Назначение

|

|

Обмен с асинхронной памятью

|

|

AD[31:0]

|

32

|

IO

|

Шина адреса и данных:

AD[31:0] ≈ разряды 31-0 передаваемых данных;

AD[31:4] ≈ разряды 31-4 адреса асинхронной памяти;

AD[14:2] ≈ разряды 12-0 адреса синхронной памяти

|

|

A[3:0]

|

4

|

O

|

Младшие разряды адреса асинхронной памяти

|

|

ALE

|

1

|

O

|

Строб адреса асинхронной памяти

|

|

nWR{3:0]

|

4

|

O

|

Запись асинхронной памяти

|

|

nRD

|

1

|

O

|

Чтение асинхронной памяти

|

|

nSTROBE

|

1

|

O

|

Строб данных

|

|

nACK

|

1

|

1

|

Готовность асинхронной памяти

|

|

nCS[2:0]

|

3

|

O

|

Разрешение выборки банков асинхронной памяти

|

|

Обмен с синхронной памятью

|

|

nRAS[1:0]

|

2

|

O

|

Строб адреса строки SDRAM

|

|

nCAS[1:0]

|

2

|

O

|

Строб адреса колонки SDRAM

|

|

nWE[1:0]

|

2

|

O

|

Разрешение записи SDRAM

|

|

DQM[3:0]

|

4

|

O

|

Маска выборки байта

|

|

SCLK[1:0]

|

2

|

O

|

Тактовая частота работы SDRAM

|

|

A10

|

1

|

O

|

10 разряд адреса внешней синхронной памяти SDRAM

|

|

BA[1:0]

|

2

|

O

|

Номер банка

|

|

ALES

|

1

|

O

|

Строб адреса синхронной памяти

|

Таблица 4. Назначение выводов управления

|

Наименование сигнала

|

Количество

|

Тип

|

Назначение

|

|

nDMAR[3:0]

|

4

|

1

|

Запрос канала DMA

|

|

nIRQ[3:0]

|

4

|

1

|

Запросы прерывания

|

|

CLK_SEL

|

1

|

1

|

Выбор коэффициента умножения частоты CLKIN:

0 - 1;

1 - 2

|

|

BYTE

|

1

|

1

|

Разрядность шины данных 6 банка внешней памяти:

0 - 32 разряда;

1 √ 8 разрядов

|

|

CLKIN

|

1

|

1

|

Сигнал тактовой частоты

|

|

nRST

|

1

|

1

|

Сигнал установки исходного состояния

|

|

TCK

|

1

|

1

|

Тестовый тактовый сигнал (JTAG)

|

|

TRST

|

1

|

1

|

Установка исходного состояния (JTAG)

|

|

TMS

|

1

|

1

|

Выбор режима теста (JTAG)

|

|

TDI

|

1

|

1

|

Вход данных теста (JTAG)

|

|

TDO

|

1

|

0

|

Выход данных теста (JTAG)

|

Таблица 5. Назначение выводов портов обмена последовательным кодом (SPORTS)я

|

Наименование сигнала

|

Количество

|

Тип

|

Назначение

|

|

DT

|

1

|

O

|

Передаваемые данные

|

|

DR

|

1

|

I

|

Принимаемые данные

|

|

TCLK

|

1

|

IO

|

Частота передачи

|

|

RCLK

|

1

|

IO

|

Частота при╦ма

|

|

TFS

|

1

|

IO

|

Синхронизация передачи

|

|

RFS

|

1

|

IO

|

Синхронизация при╦ма

|

Таблица 6. Назначение выводов UART

|

Наименование сигнала

|

Количество

|

Тип

|

Назначение

|

|

IO[7:0]

|

8

|

IO

|

Порт ввода/вывода

|

Таблица 7. Назначение выводов электропитания

|

Наименование сигнала

|

Количество

|

Тип

|

Назначение

|

|

VCC

|

16

|

1

|

Напряжение электропитания

|

|

GND

|

16

|

1

|

Земля

|

Таблица 8. Перспективные технологии проектирования и изготовления микросхем серии МС-11

|

Микросхема МС-11xx

|

Технология изготовления

|

Технология проектирования

|

|

МС-11T*

|

0,54-мкм, 5 В, производство ОАО "Ангстрем" (Зеленоград)

|

масштабируемые библиотеки ОАО "Ангстрем"

|

|

МС-11A**

|

0,52-мкм, 5/3,3 В, производство ОАО "Ангстрем" (Зеленоград)

|

масштабируемые библиотеки ОАО "Ангстрем"

|

|

МС-11B**

|

0,25-мкм, 3,3 В, производство TSMC (Тайвань) с последующим изготовлением на производстве "Ангстрем - М" (Зеленоград)

|

масштабируемые библиотеки макроблоков для перспективного отечественного производства "Ангстрем - М"

|

|

МС-11C**

|

0,35-мкм, 3,3 В, производство TSMC (Тайвань) с последующим изготовлением на производстве "1X1" (НИИСИ РАН)

|

масштабируемые библиотеки макроблоков для перспективного отечественного производства "1X1"

|

*) Опытные образцы - IV квартал 2002 года.

**) Планируется получить опытные образцы в 2003 году при обеспечении финансирования.

Таблица 9. Частота синхронизации и пиковые производительности для микросхем серии МС-11xx при нормальных условиях эксплуатации и в диапазоне температур от √60 до +125оС и при изменении напряжения питания 10%*

|

Формат представления данных, бит

|

Пиковая производительность для данных в фиксированных форматах, в млн.оп./c (MOPS)

|

Пиковая производительность для данных в форматах с плавающей точкой, млн.оп./c (MFLOPS/MMACs)

|

|

8

|

16

|

32

|

32E16

|

24E8, IEEE754

|

|

При нормальных условиях эксплуатации

|

|

МС-11T (50 МГц)

|

400

|

150

|

113

|

19

|

-

|

|

МС-11A (66 МГц)

|

528

|

198

|

149

|

25

|

-

|

|

МС-11B (160 МГц)

|

1280

|

480

|

360

|

60

|

-

|

|

MC-11C (100 МГц)

|

800

|

300

|

225

|

38

|

-

|

|

В диапазоне температур от √60 до +125 С и при изменении напряжения питания 10%

|

|

МС-11A (37МГц)

|

296

|

111

|

83

|

14

|

-

|

|

МС-11B (90 МГц)

|

720

|

270

|

202

|

34

|

-

|

|

MC-11C (56 МГц)

|

448

|

168

|

126

|

21

|

-

|

*) Представленные значения параметров носят предварительный характер и могут быть уточнены в ходе выполнения ОКР с уч╦том возможностей технологического процесса их изготовления на отечественном или зарубежном микроэлектронном производстве.

Таблица 10. Сравнительные характеристики Мультикор-11 и TMS320VC5470

|

Характеристика

|

Мультикор-11

|

TMS320VC5470

|

|

Архитектура

|

Микроконтроллер, состоящий из RISC-ядра (центральный процессор)и DSP-ядра - акселератора

|

Процессор, состоящий из двух независимых CPU: DSP и RISC

|

|

RISC-ядро

|

32-разрядный процессор MIPSI ISA архитектуры. 50 МГц

|

32-разрядный процессор типа ARM7TDMI. 47,5 МГц

|

|

DSP-ядро

|

Программируемое 32-разрядное DSP с фиксированной точкой, 50 МГц. Обеспечивает обработку широкополосных сигналов/изображений в реальном времени: фильтрация, включая адаптивную, FFT, декодер Витерби и так далее. Блочная плавающая точка, плавающая точка (16E16) и (32E16). Регистровый файл (32Wx16b 8 портов) для высокоэффективного обрабатывающего конвейера

|

16-разрядное TMS320C54x ядро с фиксированной точкой, 100 МГц. Функциональные устройства:

ALU, MAC, два аккумулятор, сдвигатель, Витебри акселератор.

Основные особенности:

два адресных генератора; аппаратная реализация циклов

|

|

Производительность DSP-ядра, млн.оп./с

|

400 - в 8-разрядном формате с фиксированной точкой;

150 - в 16-разрядном формате с фиксированной точкой;

63 - в 32-разрядном формате с фиксированной точкой;

19 (программно) - в формате с плавающей точкой 32E16

|

100 - в 16-разрядном формате

|

|

КЭШ команд RISC-ядра, Кбайт

|

2

|

Отсутствует

|

|

Внутреннее ОЗУ RISC-ядра, Кбайт

|

8

|

16

|

|

Внутренние ОЗУ DSP-ядра, Кбайт

|

4 - ОЗУ данных

8 - ОЗУ команд

|

64 - ОЗУ данных

80 - ОЗУ команд

|

|

Шины внешней памяти

|

32-разрядная шина RISC-ядра

|

32-разрядная шина RISC-ядра

16-разрядная шина DSP-ядра

|

|

Тип внешней памяти

|

Статическая SRAM/Flash

Синхронная SDRAM (до 128 Мбайт). Встроенный контроллер обеспечивает пропускную способность между внутренней и внешней памятью до 240 Мбайт/с

|

Статическая SRAM/Flash

Синхронная SDRAM (до 32 Мбайт)

|

|

Поддержка DMA

|

8 каналов DMA, 4 внешних сигналов запроса DMA. Все каналы DMA обеспечивают режим самоинициализации

|

6 каналов DMA

|

|

Программируемые таймеры

|

32-разрядный таймер

|

3 16-разрядных таймера

|

|

Наличие внешних портов

|

2 последовательных порта, совместимых с SHARC.

Универсальный асинхронный порт (UART).

8-разрядное поле флагов

|

2 последовательных порта типа McBSPs.

Универсальный асинхронный порт (UART).

Последовательный интерфейс SPI.

Контроллер шины I2C.

36-разрядное поле флагов

|

|

Режим энергосбережения

|

Останов DSP-ядра. Уменьшение внутренней тактовой частоты. Полное отключение внутренней тактовой частоты. Перевод внешней SDRAM в режим Power-down

|

Останов DSP-ядра. Уменьшение внутренней тактовой частоты. Полное отключение внутренней тактовой частоты

|

|

Наличие встроенных средств отладки программ

|

Имеются встроенные средства отладки программ (OnCD)

с интерфейсом JTAG, обеспечивающие: точки останова по содержимому программного сч╦тчика; точки останова по адресу памяти данных; доступ к конвейеру программного сч╦тчика по чтению; доступ по записи и чтению к программному сч╦тчику; выполнение трассы; запись и чтение данных по любому адресу

|

Имеются встроенные средства отладки программ с интерфейсом JTAG

|

|

Напряжение питания, В, ±10%

|

5

|

3,3

|

|

Наличие PLL

|

Имеется

|

Имеется

|

|

Средства разработки

|

Инструментальное ПО MultiCore Studio (MCS) - под Windows и Linux

|

TMS320 DSP Algorithm Standard Developers Kit.

C5000 Code Composer Studio Integrated Development Enviroment (IDE)

|

Программное обеспечение для микросхем платформы МУЛЬТИКОР

Параллельно, не дожидаясь появления кристалла и, учитывая большой интерес, который проявлен к нашей разработке со стороны потенциальных отечественных потребителей, ЭЛВИС разрабатывает первую версию базового программного обеспечения платформы МУЛЬТИКОР, которую мы сможем предоставить пользователям в IV квартале этого года.

На базе разработанного RISC-ядра MIPS1 архитектуры для СБИС СМК под WINDOWS и LINUX созда╦тся ПО, которое включает интегрированную среду программирования, несколько аппаратно-программных отладчиков, прикладные библиотеки.

Инструментальное ПО будет включать ассемблерные средства программирования обоих ядер и Cи-компилятор СБИС, программный симулятор кристалла MC-11xx (включая симуляторы всех ядер и устройств ввода/вывода, а также кристалла в целом), базовый пакет прикладных программ, а также аппаратно-программный отладчик на базе XILINX FPGA прототипа СБИС МС-11 (IV квартал 2002 г.).

Для микросхем Мультикор разработана интегрированная среда проектирования программного обеспечения (MCS - MULTICORE Studio), которая должна обеспечивать полный цикл разработки и отладки программ и функционировать под LINUX и MS Windows. Данное ПО проходит в настоящий момент стадию тестирования.

Интегрированная среда проектирования MCS включает:

- среду разработки программ RISC- и ЦПОС-ядер;

- среду отладки программ в исходных текстах, исполняемых на программном симуляторе или на макетной плате, или отладчик для работы с целевым устройством через JTAG;

- средства программного моделирования;

- интегрированную среду проектирования, представляющую пользователю доступ ко всем инструментам из одного интерфейса.

Среда разработки программ для RISC-ядра включает:

- компилятор с языка Си с препроцессором;

- ассемблер с препроцессором;

- дизассемблер;

- линковщик;

- библиотекарь;

- утилиты подготовки исполняемого кода.

Среда разработки программ для ЦПОС-ядра включает:

- ассемблер с препроцессором;

- дизассемблер;

- линковщик;

- библиотекарь;

- утилиты подготовки исполняемого кода.

Работа над программным симулятором MIPS-ядра, входящего в состав кристаллов (а также аппаратно-программного отладчика на базе FPGA-прототипа), будет завершена в IV квартале 2002 г. Это позволит пользователям начать отладку их алгоритмов на Си, не дожидаясь появления кристалла, так как симулятор MIPS-ядра обеспечит выполнение всех алгоритмов совершенно идентично тому, как они будут выполняться и на RISC-ядре СБИС МС-11xx.

С другой стороны, используя ассемблерные средства программирования DSP-ядра, можно оценить все критические места Ваших алгоритмов, представленные на языке ассемблера DSP-ядра, используя как программный симулятор ядра акселератора, так и FPGA аппаратно-программные отладчики DSP-ядра и СБИС в целом.

Перспективные модули и микросборки на базе микросхем платформы МУЛЬТИКОР

ЭЛВИС приступил к проектированию ряда процессорных модулей обработки в стандарте PC-104Plus на базе микросхем платформы МУЛЬТИКОР, которые, как предполагается, сначала будут реализованы на базе VIRTEX прототипа СБИС МС-01 (IV квартал 2002 года), а затем и изготовленного кристалла (I√II квартал 2003 г.). Модули предназначены как для работы в составе аппаратно-программного отладчика инструментального и прикладного ПО (в конструктивном исполнении PC), так и в стандарте PC-104Plus.

Рассматриваются также перспективные варианты поставки микросхемы МС-11T в составе микросборочной конструкции с высокой плотностью упаковки бескорпусных микросхем (HDP-технология, аналогичная используемой фирмой Боинг) и со встроенной в составе корпуса внешней памятью SDRAM плюс ИМС FLASH.

Рассматриваются также перспективные конструкции для удвоенной и квадро-конфигурации микросхемы МС-11T, объединяющие в одном корпусе две√четыре микросхемы МС-11T.

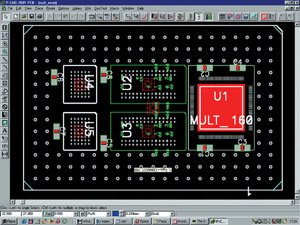

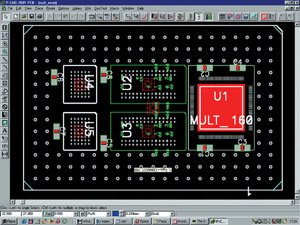

На рис. 4 привед╦н внешний вид (без крышки) микромодуля mMC-11T на базе микросхемы МС-11Т.

Рисунок 4. Плата микромодуля mMC-11T

Микромодуль mMC-11T содержит микросхему MC-11T, SDRAM 64 Мбайт и FLASH 8 Мбайт. Он размещается в корпусе размером 40x60 мм. Предполагается, что на одной двухсторонней плате PC-104Plus может быть установлено до четыр╦х таких модулей.

Состояние проекта МУЛЬТИКОР

Опытные образцы микросхем МС-11Т ожидаются в IV квартале 2002 года.

В настоящее время завершается разработка RTL-модели микросхемы с плавающей точкой (МС-02B). Данная микросхема при реализации по технологии 0,25-мкм обеспечит пиковую производительность не менее 2 млрд. операций с плавающей точкой, что соответствует уровню лучших мировых СБИС.

В серии микроконтроллеров мини-конфигурации MC-12xx также завершается проектирование первых образцов ИМС МС-12A (Ангстрем, 0,52-мкм) и МС-12B (TSMC, 0,25-мкм).

Приборы данной серии будут отличаться от ИМС серии MC-11xx, во-первых, новым RISC-ядром (RISCore-01, совместимым по программному обеспечению c MIPS32), во-вторых, новым DSP-ядром (с плавающей точкой в стандарте IEEE754√ELCORE√2) и, наконец, в-третьих, добавленными SHARC-совместимыми (ADI) байтными линками.

Запуск в изготовление опытных тестовых образцов СБИС МУЛЬТИ-КОР-01/02 миди-конфигурации по технологии 0,52 мкм (0,35 или 0,25 мкм) при наличии инвестиций может быть выполнен на ОАО "Ангстрем" или на TSMC в 2003 г. по результатам измерений микросхемы МС-11Т.

Созда╦тся библиотека ядер для мультимедийно-коммуникационного процессора "МУЛЬТИКОМ" для мобильных применений на базе миди-конфигурации СБИС-платформы МУЛЬТИКОР (MCom-xx), разрабатываемого по заказу РАСУ в рамках Федеральной программы "Национальная технологическая база" (раздел "Микроэлектронные технологии").

Исследуется возможность создания на базе платформы МУЛЬТИКОР СБИС графического процессора 3D и процессора для цифрового мультимедийного телевизора.

В настоящее время ЗАО НЦ "Ангстрем-СБИС" выполняет проектирование топологии всех заказных блоков, а ЭЛВИС выполняет схемотехническое проектирование, используя масштабируемые библиотеки.

К концу года планируется также получение первой версии инструментального программного обеспечения для СБИС на базе платформы "МУЛЬТИКОР". Она будет включать: программный Симулятор СБИС Мультикор-01 под Win98/2K и Linux, Си-компилятор для MIPS RISC-ядра, ассемблерные средства программирования DSP-ядра "ЭЛКОР-1", базовую прикладную библиотеку для DSP-ядра и МС-11/01, планируется разработка аппаратно-программного отладчика СБИС на базе его FPGA-прототипа и микросборочных конструкций.

Базовая рабочая версия инструментального программного обеспечения будет разработана в 2003 году.

Разрабатываются модули и микросборочные конструкции на базе СБИС серии МУЛЬТИКОР.

|

Время кентавров: Микросхемы серии Мультикор-11xx (MC-11xx) для встраиваемых и мобильных применений

Время кентавров: Микросхемы серии Мультикор-11xx (MC-11xx) для встраиваемых и мобильных применений