|

А. Гольдшер, П. Дик, Ю. Докучаев, В. Кучерский Микросхема управления диодными нагрузками А 1211Микросхема А 1211 (ИС) предназначена для преобразования ТТЛ-уровней в противофазные сигналы, необходимые для управления диодными нагрузками. Основные характеристики:

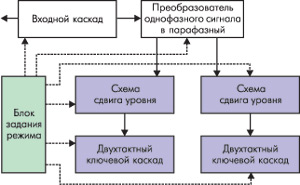

Функциональное назначение микросхемы, требования к е╦ параметрам и режимам эксплуатации предопределили структурную схему ИС. Она приведена на рис. 1. Рисунок 1. Структурная схема ИС А 1211

В частности, согласование с ТТЛ входными сигналами обусловило необходимость использования одного из известных вариантов стандартных ТТЛ (ТТЛШ) входных каскадов [1]. Дифференциальная нагрузка потребовала наличия в ИС блока преобразования однофазного входного сигнала в парафазные. Парафазные сигналы через согласующие элементы сдвига уровня подаются на выходные каскады, формирующие двухполярный выходной ток в резистивно-диодной нагрузке. К выходным каскадам предъявляется ряд специфических требований, определивших их структуру. Известные схемотехнические решения их реализации или не обеспечивают симметрию выходных импульсов относительно шин питания [2], или же характеризуются большой потребляемой мощностью и одновременно низким быстродействием из-за ограниченного усиления выходных транзисторов [3]. На рис. 2 представлена упрощ╦нная принципиальная схема двухтактного ключевого выходного каскада, предложенная авторами. Она содержит фазоинвертор с динамической нагрузкой на транзисторе VT2, верхнее плечо на VT3 и VT5, нижнее плечо на VT6 и элементы защиты от сквозных токов на VD1, VD2. Рисунок 2. Упрощ╦нная принципиальная схема двухтактного ключевого выходного каскада

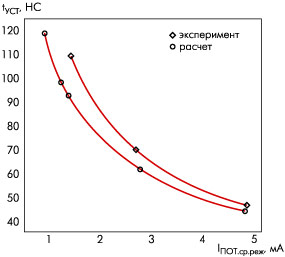

Установившееся значение выходного напряжения высокого уровня UOH определяется напряжением источника питания UCC1 за вычетом напряжения насыщения коллектор-эмиттер транзистора VT4 и напряжения на прямосмещ╦нном переходе база-эмиттер VT5. Выходное напряжение низкого уровня UOL зада╦тся напряжением источника UCC2 за вычетом напряжения насыщения коллектор-эмиттер транзистора VT6 и напряжения на прямосмещ╦нном диоде VD2. Следовательно, предложенная схема обеспечивает одно из важнейших требований, предъявляемых к ИС управления диодными нагрузками, - максимальный размах и симметрию выходных сигналов. Особенность схемы состоит в том, что положительный перепад выходного напряжения формируется в два этапа: а) ускоренное нарастание за сч╦т каскадного соединения транзисторов VT3 и VT5; б) дополнительное увеличение выходного уровня после выключения VT3 транзистором VT5 и генератором тока на VT4. За сч╦т этого достигается высокое быстродействие, сопоставимое со схемой на составных транзисторах [2]. Выполнение элементов сдвига уровня на торцевых p-n-p-транзисторах позволило обеспечить "гибкий" выбор напряжений источников питания (без ухудшения динамических параметров ИС). Регулируемый блок задания режима позволяет оптимизировать энергетические и динамические характеристики, в зависимости от конкретного применения ИС в аппаратуре. Это достигается пут╦м подключения внешнего резистора Rрег. В частности, при минимальных средних токах потребления IПОТ.ср.реж., равных 1,5 и 3,0 мА для А 1211А и А 1211Б, соответственно, величины tуст. ~150 нс. Микросхема содержит три преобразователя уровней на одном кристалле, два из которых объединены по источнику питания UCC1, а один - автономен. В качестве элементной базы ИС использованы n-p-n высокочастотные транзисторные структуры, преимущественно с диодами Шоттки, и p-n-p торцевые транзисторы, в том числе многоколлекторные [4]. В основу технологического процесса изготовления ИС положена планарно-эпитаксиальная технология с изоляцией элементов обратно-смещ╦нным p-n-переходом. При этом изолирующая диффузия бора осуществляется с использованием сильнолегированных p+-сло╦в (Ns ~ 5·1020 ат./см³) и с сохранением боросиликатного стекла, что, по сравнению с обычно применяемыми режимами (Ns ~ 4·1018 ат./см³), позволило уменьшить ╦мкость изолирующих p-n-переходов примерно в 1,5 раза за сч╦т уменьшения составляющей, обусловленной ╦мкостью боковых стенок [5]. К технологическим особенностям ИС следует также отнести:

Основные параметры ИС приведены в таблице. На рис. 3 приведены экспериментальные и расч╦тные зависимости усредн╦нного времени установления выходных сигналов tуст от величины среднего режимного тока IПОТ.ср.реж для микросхемы А 1211А. Рисунок 3. Зависимость времени установления выходного сигнала tуст от величины среднего режимного тока

Параметры моделей для расч╦тов выбирались с уч╦том электрофизических и топологических характеристик транзисторных структур. Однако, в используемых моделях не учитывались нелинейность емкостей переходов от напряжения, а также процессы накопления носителей при насыщении транзисторов. Правда, последний эффект, по всей видимости, в меньшей степени сказывался на результатах расч╦тов, так как в разработанных ИС преимущественно использованы транзисторные структуры с диодами Шоттки. В точке, соответствующей максимальному быстродействию, совпадение экспериментального и расч╦тного результатов достигалось пут╦м подбора врем╦н прол╦та неосновных носителей через базу p-n-p-торцевых транзисторов, tTN, поскольку задержки формирования выходных импульсов в микросхеме в значительной степени определяются передачей сигналов через схемы сдвига уровня, выполненные на их основе. Наиболее близкое к эксперименту значение было получено при tTN ~ 20 нс. При уменьшении режимного тока ИС расч╦тные характеристики оказываются лучше экспериментальных примерно на 20%. Конструктивно микросхемы выполнены в корпусе Н06.24-2b с планарным расположением выводов. Возможна поставка ИС и в бескорпусном исполнении (модификация 4). Таблица. Основные параметры микросхем А 1211

Литература

|

||||||||||||||||||||||||||||||||||||||||

Микросхема управления диодными нагрузками А 1211.

Микросхема управления диодными нагрузками А 1211.