|

А. Строгонов Проектирование топологии заказных КМОП БИС

В мире интерес к заказным БИС достаточно велик, и год от года он продолжает неуклонно расти. Наблюдается активное смещение "центра тяжести" в сторону изделий системного уровня интеграции, когда в кристалл интегрируется стандартное фиксированное ядро массового применения (микроконтроллер, драйвер, периферийные контроллеры, массивы памяти и так далее). Специфика разработки заказной БИС требует конструирования кристалла полностью "с пустого места" - без предварительной подготовки базовых технологических сло╦в, специально сконструированных элементов и функциональных макроблоков, возникает необходимость проектировать единые маски для всех технологических сло╦в. Разработка физических библиотечных элементов - топологий цифровых схем - и ручное уплотнение библиотеки ячеек имеют важное значение, так как позволяют повысить кремниевую эффективность (уменьшить площадь кристалла). При этом заказчик является владельцем как конечного продукта, так и заложенной в него идеи и, следовательно, нес╦т всю тяжесть и ответственность принятия решения. Именно поэтому высокие требования предъявляют к качеству подготовки инженеров - разработчиков заказных БИС. Фирма-производитель готовых микросхем выступает как исполнитель идеи проекта, которую приносит заказчик. С повышением степени интеграции общая тенденция проектирования цифровых БИС будет заключаться в стирании существующих различий между этапами чисто "логического" и "схемотехнического" проектирования - будут использоваться новые методы разработки на основе более высокой степени абстракции, с использованием современных САПР, и новые методы структурной организации БИС, таких как "система на кристалле". Так, для специалистов по БИС понятие однокристальной системы - SoC (System on chip) - означает использование для интеграции в проект внутренних, внешних продуктов заказчика, то есть размещение на одном кристалле фиксированного сложного микропроцессорного ядра, включая оперативную память для хранения программ и данных, а также достаточного объ╦ма программируемой логики для специализации кристалла пользователем под конкретную задачу. Стандартные изделия класса SoC обеспечивают комбинацию гибкости проектирования и скорости выхода конечной продукции на рынок без привлечения значительных инвестиций на начальном этапе. Обязательным условием реализации этих тенденций будет являться непрерывное усложнение объектов схемотехники, а также совмещение аналоговых и цифровых функций. Использование более эффективных схемотехнических решений по сравнению с традиционными позволяет в большинстве случаев обеспечить достижение более высоких технических параметров БИС быстрее и с меньшими затратами, чем этого можно ожидать при совершенствовании технологии изготовления БИС. Существует важная задача проектирования БИС - разработка топологий интегральных схем. Крупные компании используют продукцию Cadence и Mentor для разработки топологии, однако ориентировочная цена рабочего места здесь составляет сотни тысяч долларов. Большинство мелких фирм использует программы СТАЛКЕР и GLE, которые были разработаны ещ╦ под DOS и за последние несколько лет не обновлялись. Параллельно группой российских и украинских программистов компании ОТ-ТО Software Group была разработана система верификации топологий ОТ-ТО и редактор топологий ОТ-ТО 2000, призванные заменить старые программы. Этот пакет занял пустующую нишу "средних" САПР для проектирования БИС и очень удачно вписался в существующую рыночную ситуацию. Наибольшую популярность у российских разработчиков БИС для разработки топологических библиотек завоевал топологический редактор LTanner из САПР Tanner EDA. Для воплощения схемотехнического решения в кремний требуется фактически редактор топологии, средства размещения и трассировки блоков, контроль геометрических (DRC) и электрических (ERC) проектных норм, сравнение топологической реализации схемы с е╦ исходным описанием (LVS), - такие возможности да╦т САПР Tanner EDA. Далее кристаллы наполняются конечной физической топологией, информация записывается в формате GDSII и переда╦тся на завод-изготовитель. Завод изготавливает набор физических шаблонов и воплощает изделие в кремнии на сво╦м оборудовании. Ответственность за функциональные характеристики БИС полностью лежит на разработчике БИС, в то время как завод гарантирует качество технологического процесса. Топология БИС - множество геометрических фигур, расположенных в различных топологических слоях. Топологические слои объединяют фигуры, которые будут перенесены на один фотошаблон. Некоторое множество фигур в одном или в нескольких топологических слоях объединяются в топологическую группу. Топологическая группа кроме геометрических фигур может содержать в себе ссылки на другие группы, формируя иерархическое описание топологии БИС. Топологический редактор позволяет либо непосредственно строить топологию, либо формировать е╦ из стандартных ячеек, содержащихся в библиотеке. Используя базу данных, редактор позволяет редактировать топологию ячеек в соответствии с конкретными требованиями. После разработки топологии отдельных фрагментов с помощью соответствующей программы в диалоговом режиме осуществляется их размещение и трассировка межсоединений. После ввода описания топологии осуществляется е╦ верификация. Программа контроля проектных норм работает непосредственно с топологией. Контроль осуществляется автоматически по значениям конструкторско-технологических требований (DRC-контроль) для используемой КМОП-технологии. Любые нарушения ограничений помечаются непосредственно на изображении топологии, выводимом на экран дисплея. После завершения DRC-контроля программа восстановления электрической схемы (LVS) преобразует описание топологии в описание электрической схемы в виде таблицы цепей (например, текстовое описание в Spice-формате). Эта таблица переда╦тся в блок верификации логических и электрических схем, где проводится перекр╦стная проверка описанной схемы на логическом и топологическом уровнях, а также повторное моделирование и верификация временных параметров. Таблица переда╦тся в программу контроля электрических проектных норм (ERC-контроль). Эта программа дополнительно использует ещ╦ и значения параметров транзисторов, полученные при восстановлении электрической схемы из топологии. В результате е╦ работы идентифицируются все нераспознанные или неправильно соедин╦нные элементы, а также все нарушения электрических проектных норм. Маршрут проектирования завершается преобразованием формата проектного файла в промежуточную форму, используемую для передачи проекта на кремниевые фабрики, например CIF-формат. Топологическая группа может включать фигуры (примитивы) следующих типов: ортогональный прямоугольник, многоугольник (со сторонами под углами, кратными 45 град.), шина (со сторонами под углами, кратными 45 град.), экспозиция (наклонный прямоугольник с произвольным (кратным 0,1 град.) углом наклона сторон), текст, линия. Примитивы первых четыр╦х типов имеют замкнутый контур и формируют рисунок на фотошаблоне. Примитивы типа текст и линия рисунка на фотошаблоне не формируют, они предназначены для создания поясняющих надписей и рисунков в топологии. Привязки групп могут быть двух типов - ячейки и итерации. Ячейка описывает единичную ссылку на группу. Итерация обеспечивает множественное обращение к ссылаемой группе в виде матрицы с заданным шагом и количеством повторений по осям координат. Топологическая группа имеет уникальное имя, каждый топологический слой имеет номер. Топологический черт╦ж является связующим звеном между проектировщиком и изготовителем БИС. Проектирование топологии - процесс преобразования электрической или логической схемы в описание послойной реализации схемных компонентов (транзисторов, диодов, резисторов) и связей между ними в многослойной интегральной структуре. Известен типовой технологический процесс и заданы конструкторско-технологические ограничения. Верификация топологии включает в себя контроль проектных норм, экстракцию (восстановление) электрической схемы из описания топологии, сравнение с исходной схемой и средства анализа найденных нарушений. Главная цель разработки топологии КМОП БИС заключается в эффективном использовании площади кристалла. Однако необходимо учитывать, что характеристики КПОП БИС, в частности, динамические, сильно зависят от паразитных емкостей и сопротивлений, определяемых топологией. Поэтому необходимо принимать компромиссные решения, которые учитывали бы оптимальное использование площади и получение хороших характеристик ИС. В КМОП БИС обычно используются прямоугольные конфигурации транзисторов, отличающиеся лишь различными отношениями ширины к длине канала, в зависимости от требуемого значения крутизны характеристик транзистора. Минимальные размеры и минимальные зазорыВыберем в качестве основной единицы измерения расстояния масштабную величину Таблица 1. Характерные значения l в масштабируемой КМОП-технологии

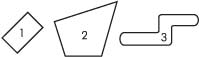

Конструкторско-технологические требования (КТТ) на процесс изготовления кристалла накладывают топологические ограничения, которые должны быть учтены при проектировании топологического рисунка ИС, например, требования минимальной ширины объектов, допустимых технологией, требования на точные размеры объектов, требования на минимальные зазоры. Промежуточная форма представления данных (CIF2.0) для описания топологии БИСПромежуточная форма представления данных CIF2.0 (сокращение от Caltech Intermediate form), разработанная в Калифорнийском технологическом институте, является средством описания графических элементарных групп (характеристик фотошаблона). Файлы в форме CIF создаются средствами САПР (топологическими редакторами, например, Ledit Tanner EDA) на базе других форм представления данных, таких как символический язык геометрической структуры (рис. 1). Идея, положенная в основу этой формы записи, состоит в литеральном описании каждого геометрического объекта с достаточной степенью точности. Рисунок 1. Различные элементарные группы в промежуточной форме CIF: 1 - прямоугольник, 2 - многоугольник, 3 - проводник

Независимо от метода проектирования топологии, полученные проекты преобразуются в форму CIF, являющуюся промежуточной формой представления данных, перед следующей трансляцией проекта применительно к различным формам выходных устройств, таких как графопостроители, устройства генерации изображений. Прямоугольник ("Box") представляется следующим образом: В 25 60 80 40 -20 20, или длина 25, ширина 60, центр 80, 40, направление -20, 20. Многоугольник ("Polygon", замкнутая область, которая определяется вершинами, заданными в требуемом порядке) представляется следующим образом: Р 00 10 20 -30 40. Проводник ("ware") представляется следующим образом: W 50 0 0 10 20 -30 40. Спецификация топологического слояКаждый простейший геометрический элемент (многоугольник, прямоугольник, проводник) должен быть обозначен пут╦м точного указания технологического фотошаблона, к которому он относится. В формате CIF для спецификации слоя используется сокращенное наименование, а в формате GDSII номер слоя (табл. 2). Наименования слоя или его номера используются в целях повышения ч╦ткости файла и для исключения необходимости согласования с многочисленными разработчиками и изготовителями БИС. Таблица 2. Условное обозначение топологических сло╦в в формате GDSII и в CIF version 2.0 (Caltech Intermediate Form) в масштабируемой КМОП-технологии

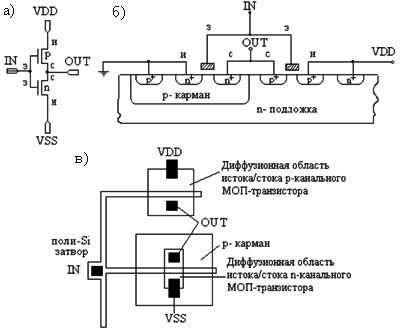

Топология инвертора по КМОП-технологииНа рис. 2 представлены электрическая схема, структура и топология КМОП-инвертора. Отличительной особенностью топологии КМОП-технологии от n-МОП технологии является наличие p-кармана. Эта область p-типа проводимости выступает в роли подложки для n-канального транзистора. Затворы n- и p-канального транзистора соединены между собой и представляют собой вход инвертора. Соедин╦нные стоки обоих транзисторов являются выходом инвертора. Исток n-канального транзистора заводится на шину Земля, а исток p-канального транзистора на шину Питание. Рисунок 2. КМОП-инвертор: а) принципиальная схема; б) поперечное сечение; в) топология инвертора с p-карманом; и - исток, з - затвор, с - сток, IN - вход, OUT - выход

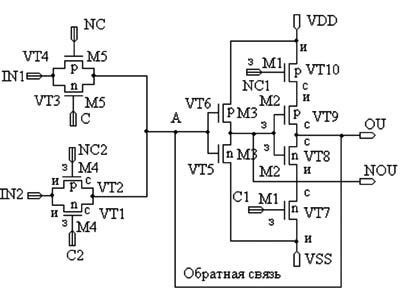

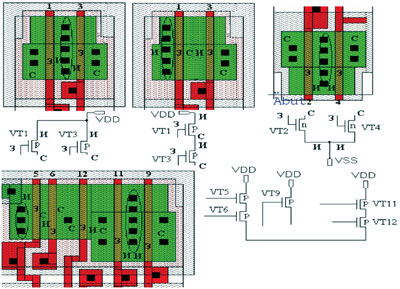

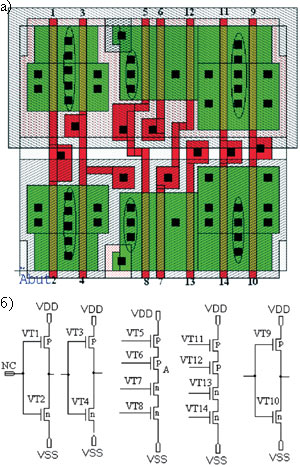

В КМОП-схемах благодаря экстремальным и фиксированным значениям логических уровней (U(0)=VSS, U(1)=VDD), не зависящих от параметров транзисторных структур (крутизна, пороговое напряжение) и, следовательно, от их топологии, отпадает необходимость топологического расч╦та на основе статических требований. Обусловленную этим свободу выбора можно использовать для проектирования КМОП-схем, обладающих топологией, которая позволяет получить оптимальные динамические характеристики - высокое быстродействие при минимальном потреблении мощности. В этом заключается принципиальное отличие топологического проектирования КМОП-схем от проектирования МОП-схем. Для минимизации потребляемой мощности необходимо уменьшать как отношение W/L, так и абсолютное значение длины канала. При расч╦те геометрических размеров транзистора длина его канала выбирается равной минимально допустимому значению - минимально допустимой ширине поликремния на n+- и p+-области. Ширину канала определяют исходя из требований, предъявляемых к крутизне. Топология МОП-транзистора с каналом p-типа по площади приблизительно вдвое больше, чем МОП-транзистора с каналом n-типа. Такая разница возникает из-за необходимости компенсации различия в подвижности дырок и электронов в тех схемах, где нужна согласованность быстродействия элементов схемы. Если в некоторых конкретных применениях согласование быстродействия несущественно, то площади транзисторов с различным типом проводимости каналов могут быть сделаны одинаковыми. Основные элементы конструкции топологии заказных КМОП БИС с одним слоем металлизацииНа рис. 3 приведена электрическая схема одноступенчатого D-триггера комбинированного типа с двумя входами, а на рис. 4 - фрагменты электрической схемы и топологии D-триггера (только n-канальные транзисторы) по 3-мкм проектным нормам с одним слоем Al металлизации. Рассматриваемый триггер состоит из двух проходных ключей на четыр╦х транзисторах VT1-VT4, инвертора на транзисторах VT5-VT6 и динамического ключ-инвертора на выходе на транзисторах VT7-VT10. На рис. 5 приведена топология D-триггера (M1, M2, M3, M4, M5 - одинаковая нумерация затворов для n- и p-канальных транзисторов дана для того, чтобы выделить комплементарную пару), используемого в кристалле микроЭВМ серии К1868 (зарубежный аналог MN1550). Рисунок 3. Электрическая схема D-триггера комбинированного типа, тактируемого уровнем

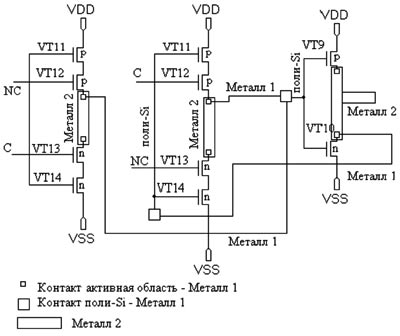

Рисунок 4. Фрагменты электрической схемы (а) и (в) и фрагменты топологии D-триггера (б) и (г)

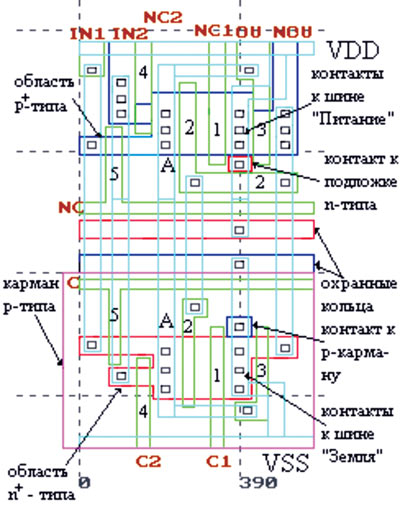

Изучая топологию D-триггера, видим, что проходные ключи (транзисторы VT1-VT4) имеют примерно одинаковое отношение W/L (размеры L и W n- и p-канальных МОП-транзисторов берутся равными минимально допустимыми для 3-мкм проектных норм). Их задача - пропустить сигнал без искажения фронтов, за время действия синхроимпульса. Особенность таких ключей: работа в однонаправленном режиме, схемы должны быть быстродействующими, ключи не имеют контактов к шинам Питание и Земля. Логический элемент на комплементарных транзисторах VT5-VT6 (затворы M3) выполнен с разными отношениями W/L p- и n-канальных транзисторов, по правилам проектирования обычного инвертора (W различны с уч╦том компенсации подвижности электронов и дырок, а длина канала L n- и p-канальных МОП-транзисторов бер╦тся равной минимально допустимой длине для 3-мкм проектных норм). Динамический ключ - инвертор на транзисторах VT7-VT10 (затворы М1-М2) - имеет наибольшее значение отношения W/L, с уч╦том токов коммутации, текущих через комплементарные транзисторы VT7, VT10 (затворы М1), для включения логического элемента на транзисторах VT8, VT9 (затворы М2). Динамические ключи имеют контакты к шинам Питание и Земля. При подаче синхроимпульсов они коммутируют (передают) на истоки транзисторов VT8, VT9 напряжения VDD и VSS, так что сложная связка транзисторов VT7-VT10 превращается в обычный инвертор. У правильно построенных транзисторов затворы (поли-Si) перекрывают ионно-имплантированные области с небольшим избытком, например, затвор M1 n-канального транзистора VT7 перекрывает с избытком n-область (рис. 4г). В противном случае, эффективность запирающего сигнала будет частично утеряна. Например, если на ж╦лтом проводнике нуль, который должен запереть ж╦лто-красную область, красный проводник не будет полностью заблокирован, так как ток может обойти стороной запирающую ж╦лтую область. Даже если ж╦лтый проводник полностью перекрывает красную область, но не имеет запаса в области перекрытия, неопредел╦нности, связанные с производством, фактически могут привести к его укорачиванию. Избыток на ж╦лтом слое в области пересечения с красным слоем гарантирует над╦жное перекрытие даже в расплывающемся изображении. Вторая особенность - это то, что синяя и красная области для предотвращения возникновения тока утечки между n- и p-канальными транзисторами имеют некий минимальный зазор. Как правило, эту область используют для прокладки токопроводящих дорожек, в данном случае это поликремниевые тактовые шины NC и C (рис. 5). Кроме того, n- и p-области отделяются друг от друга охранными кольцами противоположного типа проводимости. Охранное кольцо p-типа заводится на шину Земля, а n-типа - на шину Питание. Смещение n-канальных транзисторов достигается следующим способом (рис. 5). Рисунок 5. Топология D-триггера по КМОП-технологии: IN1, IN2 - сигнальные входы; NC, C, NC1, C1, NC2, C2 - тактовые входы; OU, NOU - выходной сигнал высокого и низкого уровня, соответственно; 1, 2, 3, 4, 5 - затворы p- и n-транзисторов

Охранное кольцо p-типа, локальная область p+ под контакт к p-карману, истоковая n-область МОП-транзисторов с помощью контактов и Al-металлизации подключаются к шине Земля. Для этого используют 5 контактов: один к охранному кольцу, один к локальной области под контакт к карману, три - к истоковой области n-МОП транзисторов. Смещение p-канальных транзисторов достигается следующим способом (рис. 5). Охранное кольцо n-типа, локальная область n+ под контакт к n-подложке, истоковая p-область МОП-транзисторов с помощью контактов и Al-металлизации подключаются к шине Питание. Для этого используют 5 контактов: один к охранному кольцу, один к локальной области под контакт к карману, три - к истоковой области p-МОП транзисторов. "Простые" логические элементы типа: инвертора, И-НЕ, (3)И-НЕ, ИЛИ-НЕ, (3)ИЛИ-НЕ - могут не иметь контактов к охранным кольцам, а "составные" типа D-триггеров и периферийных ячеек, например, инвертор с третьим состоянием, - имеют контакты ввиду повышенных паразитных токов утечек. Проходные ключи в ядре БИС используются только в однонаправленном режиме. Для рассматриваемой технологии с p-карманом они формируются по следующему правилу: исток n-канального транзистора соедин╦н с истоком p-канального и, наоборот, сток n-канального соедин╦н со стоком p-канального (рис. 3 и 4). В данной топологии D-триггера выход NOU (затвор М3, стоковая область транзистора VT6) и вход IN2 (затвор М4, истоковая область транзистора VT2) конструируются p-областью, а выход OU (узел А, затвор М3 транзистора VT6) и вход IN1 (затвор M5, истоковая область транзистора VT4) - поликремниевым. Таким образом, ячейка D-триггера спроектирована так, что е╦ интерфейс (входы, выходы), за исключением тактовых сигналов, находится со стороны p-канальных МОП-транзисторов. Это позволяет размещать топологические ячейки в ряды. Образующиеся строки со стороны p-канальных транзисторов используются для прокладки сигнальных проводников (входные и выходные сигналы), прич╦м в строках используются три вида проводников: металл, поли-Si, p+-область, которые могут пересекаться между собой, не образуя электрических соединений. Обратная связь в топологическом представлении реализована физическим контактом (стоки транзисторов проходных ключей транзисторов VT1-VT4, стоки транзисторов VT8, VT9). Далее с помощью Al-металлизации, двухконтактных окон к затворам M3 транзисторов VT5, VT6 и тр╦х к p- и n-области стоков транзисторов проходных ключей и стоков транзисторов VT8, VT9. На рис. 6 приведена топология двухтактного D-триггера (разряд сч╦тчика без занесения данных), используемого, например, в двоичных 4-разрядных сч╦тчиках. Электрическая схема D-триггера показана на рис. 7. Для данного триггера предусмотрен вспомогательный вход Set (установка), предназначенный для прямой установки триггера, и обозначается буквой S. Рисунок 6. Топология статического двухтактного D-триггера с асинхронным входом S

Рисунок 7. Электрическая схема статического двухтактного D-триггера с асинхронным входом установки Set

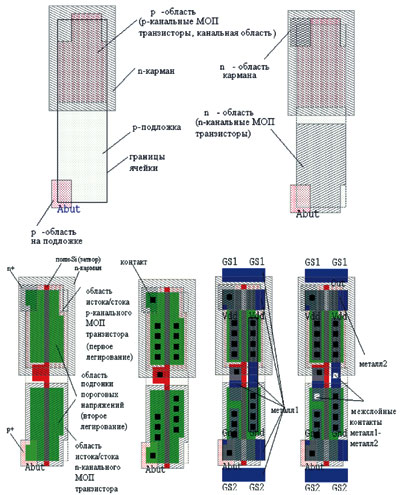

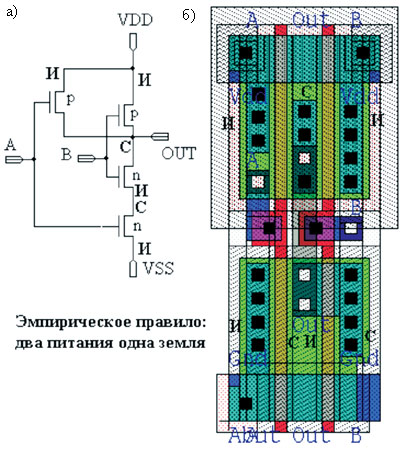

Основные элементы конструкции топологии заказных БИС по КМОП-технологии с двумя слоями металлизацииГлавная проблема при создании КМОП СБИС с длиной канала 1 и менее микрон - это сквозное обеднение, при котором обедн╦нные области истока и стока перекрываются друг с другом, и под областью канала может возникать цепь для протекания тока. Решить эту проблему позволяет повышение примесной концентрации только на том участке, где возможно перекрытие областей. Локальное повышение примесной концентрации можно получить с помощью второго легирования примесными ионами с более высокой энергией (эта операция называется подгонка пороговых напряжений). Первое легирование позволяет получить канальные области p- и n-МОП транзисторов. Второе легирование, проводимое после формирования затворного окисла (введение примесных атомов в область канала), позволяет установить заданное значение заряда обедн╦нного слоя. Такие МОП-транзисторы с двойным ионным легированием представляют собой элементарную базу так называемых высококачественных КМОП (HCMOS) ИС. Металл 1 служит для создания внутренних межсоединений в топологических ячейках и для прокладки шин "Питание" и "Земля", тактовых шин. Металл 1 прокладывается горизонтально или вертикально. Топологический слой металл 2 служит для прокладки входных и выходных сигналов и частично для внутренних межсоединений. Металл 2 прокладывается вертикально. Рассмотрим порядок формирования топологии (топологических сло╦в) инвертора по КМОП-технологии с p-карманом. Топология инвертора послойно представлена на рис. 8. Топология ячейки строится в следующем порядке:

Рисунок 8. Фрагменты топологии инвертора по КМОП-технологии с n-карманом

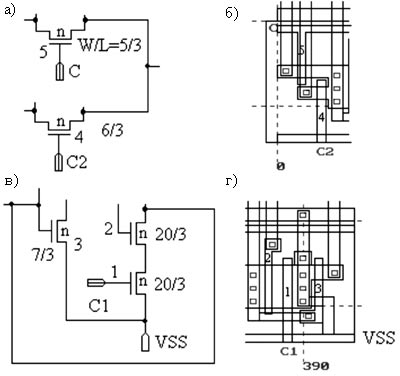

Первое легирование позволяет сформировать канальные области p- и n-МОП транзисторов. Второе легирование, проводимое после формирования затворного окисла (введение примесных атомов в область канала), позволяет установить заданное значение заряда обедн╦нного слоя. Такие МОП-транзисторы с двойным ионным легированием представляют собой элементарную базу так называемых высококачественных КМОП (HCMOS) ИС. Варианты соединений транзисторов и их топологическая реализация представлены на рис. 9. Быстро распознать топологию логических элементов 2И-НЕ 2ИЛИ-НЕ позволяет следующее правило: для схемной реализации логического элемента 2И-НЕ необходимо два контакта к шине Питание ("запитываются" два истока p-канальных транзисторов) и один контакт к шине Земля ("заземляется" один исток n-канального транзистора); для логического элемента 2ИЛИ-НЕ необходимо "одно питание две земли". В топологической реализации вентилей используют три или более контактов к истоковым областям транзисторов, для того чтобы над╦жно соединить шины Питание и Земля. На рис. 10 приведена топологическая реализация элемента 2И-НЕ. Изучая топологию, видим две группы контактов к истоковым областям p-канальных транзисторов (слева и справа две n-области для смещения кармана) и два "отвода" шины Питание (два вертикально расположенных бокса шины Питание), одну группу контактов к истоковой области n-канального транзистора (слева p-область для смещения подложки) и один "отвод" шины Земля (один вертикальный бокс шины Земля). Рисунок 9. Варианты соединений транзисторов и их топологическая реализация

Рисунок 10. Электрическая схема (а) и топологическая реализация элемента 2И-НЕ (б)

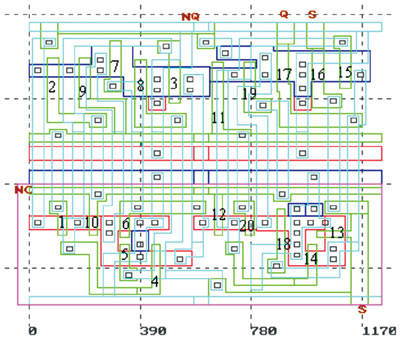

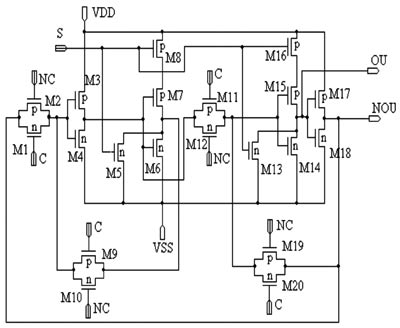

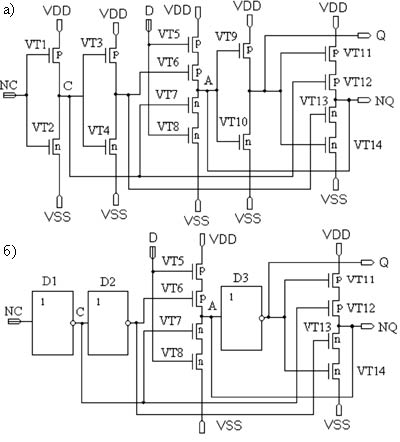

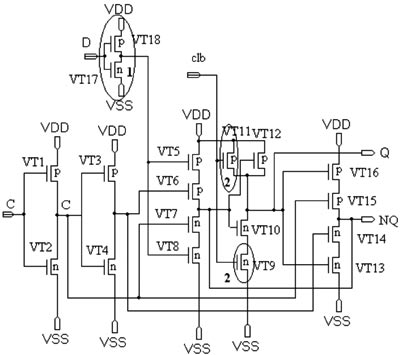

Топологические особенности построения D-триггеров с двумя слоями металлизацииНа рис. 11 показан динамический D-триггер, тактируемый одним синхросигналом С, представленный в удобном для топологической реализации виде и адаптированный к системе с однофазной синхронизацией. Для этого в схему введены дополнительные инверторы. Рисунок 11. Исходное описание электрической схемы однотактного D-триггера (защ╦лки) на основе динамических ключей с одним синхровходом: а) реализация D-триггера на вентильном уровне; б) реализация D-триггера на уровне логических элементов

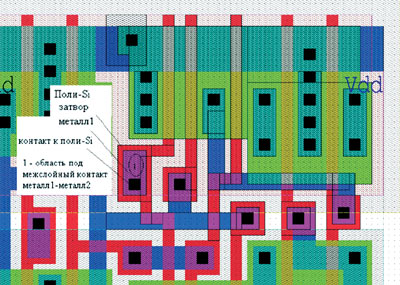

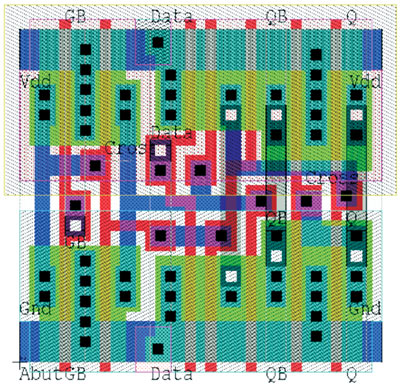

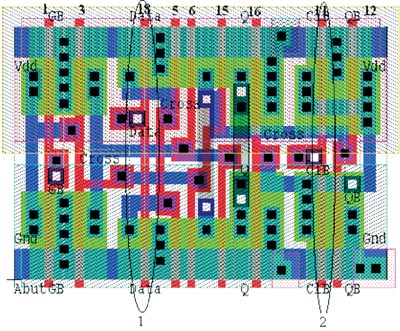

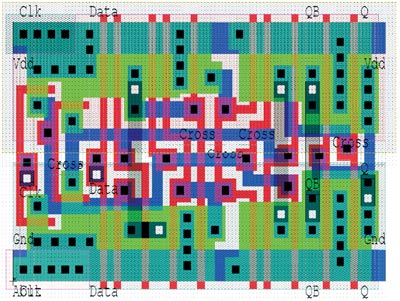

На рис. 12а представлена топология динамического D-триггера без сло╦в: металл 1, межслойных контактов металл 1 - металл 2, металл 2. Затворы транзисторов пронумерованы цифрами 1, 2, 3┘ в соответствии со схемой на рис. 11. Видно, что геометрические размеры (длина и ширина каналов) n- и p-МОП транзисторов выполнены примерно одинаковыми. Часть внутренних межсоединений выполнены поликремнием (например, затвор транзистора VT12 и затвор транзистора VT7 связаны между собой поликремнием). Три и более контактных окон в активном слое предназначены для подключения шин Питание и Земля (на рис. 12 они обведены эллипсом). Затворы транзисторов VT1, VT2 и VT5, VT8 выполнены большим "лаптем" с последующим расчетом, что это будут входы тактового сигнала NC (C) и сигнала Data (D), которые прокладываются вторым металлом (топологический слой металл 2) вертикально. Размеры "лаптя" рассчитываются на два контактных окна: контакт поликремниевый затвор - металл 1; контакт металл 1 -металл 2, по правилам КТТ. На рис. 12б показано расположение логических элементов триггера, согласно его топологической реализации. Рисунок 12. Топология D-триггера без сло╦в: металл 1, межслойных контактов, металл 2 (а) и расположение логических элементов, восстановленных из описания топологии (б)

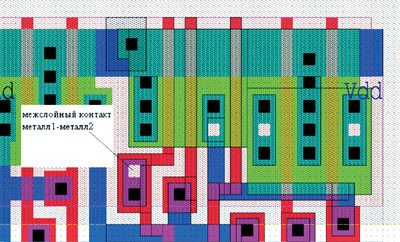

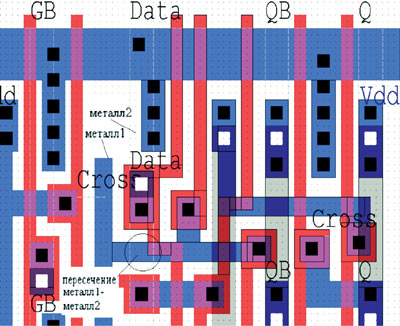

На рис. 13 и 14 показано, как формируется межслойный контакт металл 1 - металл 2. Вначале формируется контакт к поли-Si затвору, далее формируется небольшой отрезок слоя металл 1 с расч╦том места под межслойный контакт металл 1 - металл 2 (рис. 14). На рис. 15 показан фрагмент сформированной структуры: поликремниевые затворы, металл 1, межслойные контакты, металл 2. Топология динамического D-триггера тактируемого уровнем показана на рис. 16. Данный топологический чертеж является базовым по отношению к возможным модификациям. На рис. 17 показан эскиз построения обратной связи в данном триггере. Обратная связь, необходимая для образования бистабильной ячейки, выполняется двумя слоями металлизации. Металл 1 соединяет стоки транзисторов VT6, VT7 c затворами транзисторов VT9, VT10. Рисунок 13. Фрагмент топологии D-триггера (без межслойных контактов и топологического слоя металл 2)

Рисунок 14. Фрагмент топологии D-триггера с межслойными контактами, без топологического слоя металл 2

Рисунок 15. Фрагмент топологии D-триггера, показаны: поликремниевые затворы, металл 1, межслойные контакты, металл 2

Рисунок 16. Топология D-триггера тактируемого уровнем

Рисунок 17. Эскиз построения обратной связи в D-триггере тактируемого уровнем, восстановленный из описания топологии

Металл 2 соединяет стоки p-МОП транзисторов VT6, VT12 и n-МОП транзисторов VT7, VT13. На рис. 18 и 19 представлена электрическая схема и топология динамического D-триггера со входом clb, выполняющего функцию установки триггера (выход Q) в состояние логической единицы. Активным сигналом в данном случае является наличие сигнала логического нуля на входе clb. Для этого вместо инвертора на транзисторах VT9, VT10 рис. 11, используется логический элемент 2И-НЕ. Схема также содержит дополнительный инвертор на входе D. Отличительные особенности схемы в топологии показаны эллипсом. Рисунок 18. Исходное описание электрической схемы D-триггер на основе динамических ключей с одним синхровходом, со входом clb

Топология схемы построена на основе топологии базовой ячейки - D-триггера и пут╦м простого добавления недостающих инверторов. На рис. 19 области, подвергавшиеся редактированию, помечены эллипсами 1 и 2. Рисунок 19. Топология D-триггера тактируемого уровнем со входом clb

На рис. 20 представлена топология D-триггера тактируемого фронтом построенного на базе двух D-триггеров тактируемых уровнем. Рисунок 20. Топология триггера тактируемого фронтом

Литература

|

Проектирование топологии заказных КМОП БИС.

Проектирование топологии заказных КМОП БИС.