|

М. Кузелин

ПЛИС фирмы Xilinx: семейство SpartanTM-3В апреле 2003 года фирма Xilinx начала выпуск нового семейства ПЛИС с архитектурой FPGA (Field-Programmable Gate Arrays) - SpartanTM-3. Семейство специально разработано для использования в электронных устройствах, рассчитанных на большие тиражи и критичных к стоимости комплектующих. Всего в семействе планируется выпускать 8 кристаллов, отличающихся логической ╦мкостью, при этом минимальный по ╦мкости кристалл содержит 50 тыс. эквивалентных системных вентилей, а максимальный - 5 млн. В табл. 1 представлены основные свойства кристаллов серии Spartan-3. Таблица 1. Основные свойства кристаллов серии Spartan-3

Семейство Spartan-3 является дальнейшим развитием семейства Spartan-IIE, при этом увеличены логические ресурсы, ╦мкость внутренней памяти, общее число пользовательских блоков ввода/вывода и системная производительность, а также улучшено управление синхронизацией. Большинство улучшений получены с использованием технологий и архитектурных решений, применяемых в производстве кристаллов семейства VirtexTM-II. Кристаллы семейства Spartan-3 производятся по КМОП-технологии с проектными нормами 90 нм и являются первыми ПЛИС, выпускаемыми по такой технологии. Данная технология позволяет получать большее количество кристаллов с одной пластины, чем предыдущая технология (130 нм), что, в свою очередь, понижает стоимость кристалла эквивалентной ╦мкости. Снижение стоимости может достигать 80%. Следствием применения новой технологии производства кремния явилась необходимость снижения напряжения питания ядра кристалла до 1,2 В. Совместимость с более "высоковольтными" стандартами ввода/вывода достигается применением дополнительного питания блоков ввода/вывода, которое может меняться от 1,2 до 3,3 В и зависит от выбранного при программировании стандарта. Всего ПЛИС семейства Spartan-3 поддерживают 17 однополюсных и 6 дифференциальных стандартов, включая LVDS. Модули, выполняющие специальные функции, также требуют дополнительного напряжения питания, которое составляет 2,5 В. Микросхемы семейства Spartan-3 планируется выпускать как в корпусах с "шариковыми" выводами, так и в корпусах с планарными выводами. Микросхемы в одном корпусе, но разной ╦мкости совместимы по назначению выводов корпуса. В табл. 2 представлены данные о количестве пользовательских контактов ввода/вывода для микросхем семейства Spartan-3 в зависимости от логической ╦мкости кристалла и типа корпуса. Таблица 2. Данные о количестве пользовательских контактов ввода/вывода для микросхем семейства Spartan-3 в зависимости от логической ╦мкости кристалла и типа корпуса

Разработка проекта на базе ПЛИС серии Spartan-3 поддерживается пакетом программного обеспечения Xilinx ISE, начиная с версии 5.2i. Существует 4 конфигурации пакета:

В табл. 3 привед╦н список микросхем, поддерживаемых каждой конфигурацией пакета. Поддержку кристаллов XC3S4000 и XC3S5000 планируется включит в пакеты ISE Alliance и ISE Foundation в версии 6.1i, которая выйдет в сентябре 2003 г. Таблица 3. Список микросхем, поддерживаемых каждой конфигурацией пакета

Обзор архитектурных особенностей Архитектура ПЛИС семейства Spartan-3 содержит 5 фундаментальных программируемых элементов:

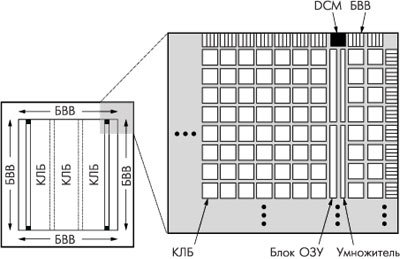

Все эти элементы расположены в кристалле, как показано на рис. 1. Блоки ввода/вывода расположены вокруг регулярной матрицы конфигурируемых логических блоков. В кристаллах от XC3S200 до XC3S2000 имеется 2 столбца модулей блочного ОЗУ, встроенных в матрицу, а в кристаллах от XC3S4000 до XC3S5000 - 4 столбца. Каждый столбец состоит из нескольких блоков памяти по 18 Кбит каждый. Каждый блок памяти ассоциирован с блоком умножения 18x18. Модули управления синхронизацией располагаются рядом с крайними столбцами памяти. Кристалл XC3S50 не имеет ни блочной памяти, ни встроенных умножителей, ни модулей управления синхронизацией.

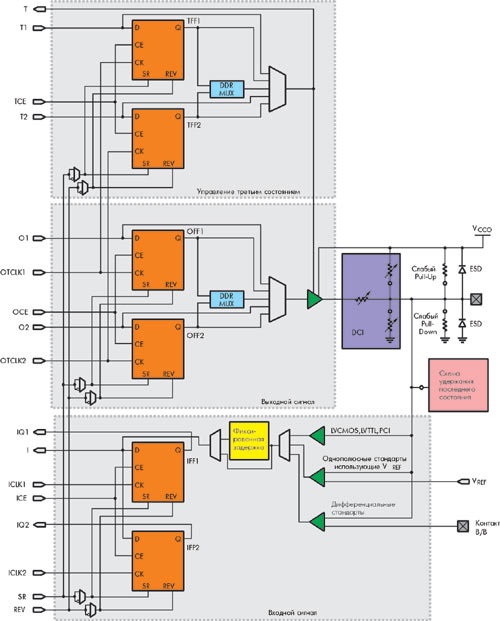

Новое поколение программируемых трассировочных ресурсов осуществляет межсоединения перечисленных выше логических элементов. Программируемые межсоединения имеют иерархическую структуру и предназначены для реализации быстродействующих проектов. Основным элементом этой иерархии является главная трассировочная матрица - ГТМ (General Routing Matrix - GRM). Она представляет собой матрицу переключающих транзисторов. Каждый программируемый элемент связан с ГТМ. Все программируемые элементы, включая ресурсы трассировки, управляются кодами, хранящимися во внутрикристальном статическом ЗУ. Эти коды загружаются во внутренние ячейки ЗУ из внешних элементов памяти после включения питания и могут перезагружаться в процессе работы для изменения функций программируемых элементов. Рассмотрим подробнее свойства основных конфигурируемых элементов кристалла. Блоки ввода/вывода (БВВ) БВВ реализует программируемый двунаправленный интерфейс между внутренней логикой кристалла и выводами корпуса микросхемы. Упрощ╦нная блок-схема БВВ представлена на рис. 2. Каждый БВВ может быть запрограммирован как:

Рисунок 2. Упрощ╦нная блок-схема блоков ввода/вывода (БВВ)

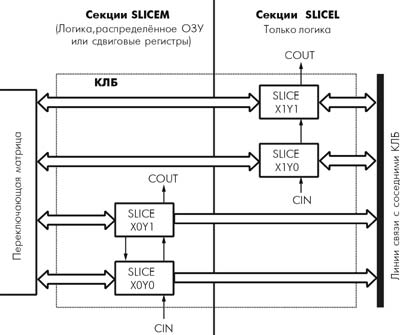

Все регистры могут программироваться либо как D-триггер, либо как триггер-защ╦лка. К линиям ввода или вывода в каждом БВВ могут быть подключены pull-up или pull-down резисторы. Задействовать эти резисторы можно на этапе создания схемы проекта, использованием библиотечных элементов PULLUP и PULLDOWN. Также это можно сделать через файл ограничений или включением соответствующих атрибутов в HDL-описание проекта. Эти резисторы могут быть подключены ко всем незадействованным контактам на этапе создания конфигурационного файла с помощью опции Unused-Pin программы Bitstream Generator (BitGen). Низкий логический уровень на служебном контакте HSWAP_EN активирует pull-up резисторы на всех контактах во время загрузки конфигурационной последовательности. В каждом БВВ имеется специальная схема удержания последнего состояния шины. Функция активируется использованием символа KEEPER. Ограничивающие диоды защищают все БВВ от повреждения электростатическим разрядом. К каждому контакту ввода/вывода подключено два диода: один замкнут на VCCO, другой на "землю". Эти ограничивающие диоды всегда подключены к контактам, независимо от того, на совместимость с каким стандартом запрограммирован БВВ. Как результат, микросхемы семейства Spartan-3 не восприимчивы к сигналам с напряжением питания более 3,45 В. Две опции, FAST и SLOW, контролируют скорость переключения выходного сигнала БВВ. FAST обеспечивает быстрое переключение, SLOW сглаживает нелинейность переключения. Данные опции применимы только для сигнальных стандартов LVCMOS и LVTTL. Для этих же стандартов возможно программирование силы тока источника на 2, 4, 6, 8, 12, 16 или 24 мА. Выбор соответствующего значения также позволяет уменьшить нелинейность переключения. Все БВВ поддерживают периферийное сканирование в соответствие со стандартом IEEE 1149.1 Программируемый импеданс (DCI) в БВВ позволяет не использовать внешних согласующих резисторов. БВВ поддерживают следующие однополюсные стандарты ввода/вывода: GTL, GTLP, HSTL_I, HSTL_III, HSTL_I_18, HSTL_II_18, HSTL_III_18, LVCMOS12, LVCMOS15, LVCMOS18, LVCMOS25, LVCMOS33, LVTTL, PCI33_3, SSTL18_I, SSTL2_I и SSTL2_II. Также БВВ поддерживают дифференциальные стандарты LDT_25, LVDS_25, BLVDS_25, LVDSEXT_25, ULVDS_25 и RSDS_25. Для каждой дифференциальной пары используются два соседних вывода. Конфигурируемые Логические Блоки (КЛБ) Конфигурируемый логический блок содержит основные логические ресурсы, необходимые для реализации синхронных или комбинаторных функций. Каждый КЛБ состоит из 4-х секций (SLICE), как показано на рис. 3. Эти секции сгруппированы в пары (SLICEM и SLICEL), каждая пара имеет независимую цепь переноса.

Все четыре секции содержат:

Все секции способны реализовать логическую или арифметическую функцию, а также ПЗУ. Кроме этого, секции SLICEM, расположенные на рис. 3 слева, могут реализовать ОЗУ и 16-бит сдвиговые регистры. Функциональные генераторы реализованы в виде 4-х входовых таблиц преобразования (Look-Up Table ≈ LUT). Кроме использования в качестве функциональных генераторов, каждый LUT-элемент, расположенный в секции SLICEM, может быть также использован как синхронное ОЗУ размерностью 16x1 бит. Более того, из двух LUT-элементов в рамках одной секции можно реализовать синхронное ОЗУ размерностью 16x2 или 32x1 бит, либо двухпортовое синхронное ОЗУ размерностью 16x1 бит. Запоминающие элементы в КЛБ могут конфигурироваться в виде динамических триггеров D-типа, чувствительных к фронту сигнала или в виде триггеров-защ╦лок, чувствительных к уровню сигнала. Каждый КЛБ имеет внутренние быстродействующие линии связи и соедин╦н с переключающей матрицей, осуществляющей доступ к глобальным трассировочным ресурсам. Блочная память Все микросхемы семейства Spartan-3, кроме XC3S50, содержат специальные программируемые блоки памяти. Каждый блок памяти представляет собой синхронное ОЗУ ╦мкостью 18 Кбит. Блоки можно каскадировать и тем самым образовывать массивы памяти большей ╦мкости. Блочное ОЗУ может применяться в проектах для хранения относительно большого количества данных с большей эффективностью, чем упомянутая выше распредел╦нная память на базе LUT-элементов. Блок памяти имеет двухпортовую структуру. Два равнозначных порта, условно обозначаемые как порт A и порт B, могут осуществлять независимый доступ к общему массиву памяти блока, ╦мкостью 18432 или 16384 бит, если используется контроль ч╦тности. Существует 4 основных способа прохождения данных через блок ОЗУ (рис. 4):

Разрядность шины данных может быть запрограммирована, при этом разрядность шины адреса может быть вычислена по формуле: R = 14 √ [log(W√P)/log(2)], где R - число разрядов шины адреса; W - общее число разрядов шины данных; P - число бит ч╦тности. Количество адресуемых слов (N), или глубину памяти, можно вычислить по формуле N = 2R. Произведение N и W да╦т общую логическую ╦мкость блока ОЗУ. В табл. 4 приведены допустимые соотношения упомянутых выше параметров блока ОЗУ. Таблица 4. Допустимые соотношения упомянутых выше параметров блока ОЗУ

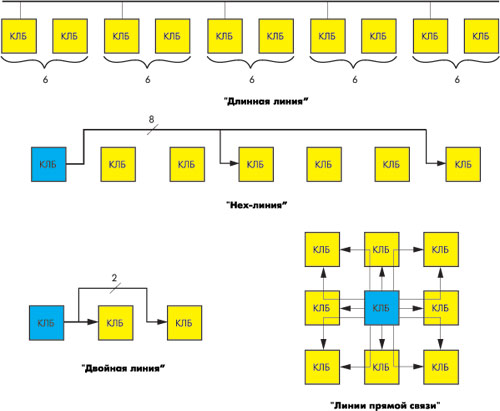

Разрядность соответствующих шин порта A и порта Б может отличаться. Блоки умножителей Блок умножителя связан с соседним блоком памяти, может выполнять функцию умножения двух 18-разрядных чисел и оптимизирован на выполнение операции с содержимым одного порта блока ОЗУ. Умножитель 18x18 может использоваться и независимо от блочной памяти. Несколько блоков могут каскадироваться и выполнять умножение чисел большей разрядности. Наличие блоков умножения позволяет эффективно реализовывать на ПЛИС семейства Spartan-3 операции считывания/умножения/суммирования и цифровой фильтрации. Цифровые блоки управления синхронизацией Во всех кристаллах семейства Spartan-3, кроме XC3S50, имеется 4 блока цифрового управления сигналами синхронизации - DCM. DCM может использоваться для подстройки фронтов внутренних или внешних тактирующих сигналов, а также для сдвига фазы тактовых частот на 90, 180 и 270 градусов. Дискретный сдвиг фазы реализует точную подстройку с шагом дискретизации, равным 1/256 тактового периода. Гибкий синтез частоты обеспечивает на выходе тактовую частоту, равную отношению М/D к входной тактовой частоте, где М - целое число в диапазоне от 2 до 32, D - целое число в диапазоне от 1 до 32. В микросхемах существует 8 глобальных тактовых входов, которые обеспечивают доступ к внутренней сети линий связи с малыми задержками. Линии связи Линии связи осуществляют электрическое соединение различных функциональных элементов ПЛИС друг с другом. Существует 4 типа линий связи: "длинные линии", "hex-линии", "двойные линии" и "линии прямой связи". На рис. 5 проиллюстрированы основные отличительные особенности каждого типа линий связи.

Конфигурирование в устройстве ПЛИС семейства Spartan-3 конфигурируются пут╦м загрузки конфигурационных данных во внутреннюю конфигурационную память, используя один из пяти режимов:

Для хранения конфигурационной последовательности фирма Xilinx выпускает два семейства ПЗУ:

В будущем планируется начать производство микросхем Flash-памяти серий XCF00S и XCF00P (табл. 5). Таблица 5. Микросхемы Flash-памяти серий XCF00S и XCF00P

В настоящее время доступны для заказа инженерные образцы микросхем XC3S50 и XC3S1000. Серийное производство всех ПЛИС семейства Spartan-3 намечено на 2004 г. Подробная информация о ПЛИС семейства Spartan-3 представлена на Интернет-сайте компании Xilinx: www.xilinx.com. |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

ПЛИС фирмы Xilinx: семейство SpartanTM-3.

ПЛИС фирмы Xilinx: семейство SpartanTM-3.