|

С. Кузнецова Новые возможности OrCAD 10.0В статье приведено краткое описание возможностей системы OrCAD для разработки проектов на базе программируемых логических устройств FPGA/CPLD. Из достоинств системы можно отметить высокую степень интеграции пакета и возможность поддержки языка описания аппаратуры Verilog. Правда, высокая стоимость продукта, а также необходимость приобретения дополнительных программных модулей NC VHDL Desktop и Synplify несколько снижают его конкурентоспособность по сравнению с системами Protel DXP компании Altium (www.protel.com) и Active-HDL компании Aldec (www.aldec.com). Весной этого года компания Cadence (www.cadence.com) выпустила новую версию системы проектирования печатных плат OrCAD 10.0 (www.orcad.com). В этой версии просматривается ряд изменений, направленных на совершенствование возможностей проектирования FPGA/CPLD интегральных схем, реализация которых была начата в версии 9.2.3. В частности, создана улучшенная среда проектирования, которая позволяет работать с программами синтеза фирмы Synplicity Synplify, с VHDL-симулятором программы Cadence NC VHDL Desktop, программами размещения и трассировки (place and route) фирм производителей микросхем Xilinx, Altera и Actel (все перечисленные программы должны быть предварительно инсталлированы на вашем компьютере). Работа с перечисленными программами осуществляется без выхода из пакета OrCAD Capture, обеспечивая непрерывный процесс проектирования устройства FPGA/CPLD, по окончании которого будет сформировано условное графическое изображение элемента для разработки печатной платы. Доработана среда Verilog проектирования. Вдобавок к уже существующим возможностям проектирования на VHDL, OrCAD Capture обеспечивает Verilog- проекты текстовым редактором с подсветкой ключевых слов и проверкой синтаксиса. Специальная функция позволяет получить список готовых конструкций Verilog, которые могут быть вставлены в файл проекта. Также значительно улучшен процесс получения Netlist для Verilog. Кратко рассмотрим процесс проектирования устройств с программируемой логикой. Перед этим введ╦м несколько определений: Проекты с программируемой логикой - это такие проекты, которые используются для разработки устройств FPGA и CPLD на базе специальных семейств микросхем различных фирм-производителей. Структура проекта - совокупность модулей, которые должны содержать информацию, необходимую для выполнения всех этапов процесса разработки устройства. Она включает в себя: исходные описания проектируемого устройства в графической или текстовой форме; промежуточные результаты, используемые в качестве исходных данных для последующих шагов проектирования; отч╦ты о выполнении основных этапов проектирования; описания тестовых воздействий, необходимых для моделирования устройства; окончательные результаты проектирования, используемые для конфигурирования элемента. FPGA (Field Programmable Gate Array) - базовые матричные кристаллы, например, устройства (кристаллы) Xilinx. CPLD (Complex Programmable Logic Device) - сложные программируемые устройства, например, устройства типа ACTEL. VHDL и Verilog - языки высокого уровня, предназначенные для описания аппаратуры HDL (High Device Language). NC Desktop simulators - программа, использующаяся в качестве средства компиляции, моделирования и отладки устройства программируемой логики, описанного на языках высокого уровня описания аппаратуры VHDL и Verilog. Synplify Synplicity - пакет программ для синтеза программируемых логических схем. Программа OrCAD Capture, в совокупности с другими продуктами Cadence, предоставляет пользователю все необходимые средства для выполнения следующих этапов процесса проектирования: входного проектирования; функционального моделирования; синтеза, размещения и трассировки; моделирования задержек; генерации элемента. При разработке проекта, включающего HDL-модели, следует помнить, что программа OrCAD Capture не поддерживает проекты на смешанных языках, а значит, все HDL-модели в проекте должны быть выполнены с использованием одного из языков: VHDL или Verilog. Создание проектаНа этой стадии осуществляется физическое проектирование, начиная от выбора технологического и библиотечного базиса. OrCAD Capture предоставляет все средства для создания функционирующего проекта в схемотехнической форме, или в VHDL- или Verilog-моделях. При этом проект не обязательно должен состоять полностью из схемотехнических или HDL-моделей, программа Capture да╦т возможность работать со смешанными проектами. Обычно на этой стадии процесса проектирования схемы создаются без расч╦та временных характеристик. Таким образом, если пользователь решил, что проект будет содержать программируемые логические матрицы, следует сразу выбрать нужный тип проекта при его создании: New / Project / Programmable Logic Wizard. Далее будет предложено выбрать тип кристалла и конкретное семейство. Список устройств, поддерживаемых версией OrCAD Capture 10.0, привед╦н в таблице. Таблица. FPGA, поддерживаемые OrCAD версии 10.0

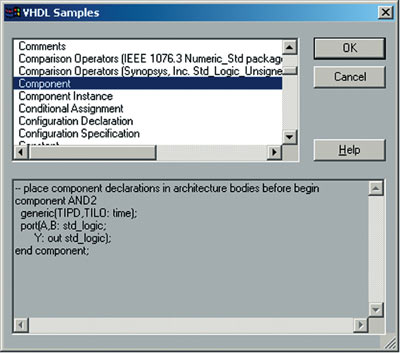

После выбора нужного типа и семейства будет создан новый проект с подключенными библиотеками логических матриц и вентилей, из которых в дальнейшем будет формироваться указанное устройство. При этом появится новая панель инструментов с командами, обеспечивающими процесс его проектирования. При работе с проектом такого типа появляются две папки PIC Resource и Simulation Resource, в них будут храниться данные для моделирования, файлы синхронизации и промежуточные списки соединений (Netlist). Структура такого проекта приведена на рис. 1. Для создания описания проектируемого устройства на языке VHDL или Verilog используется встроенный редактор этого языка, при этом ключевые слова подсвечиваются, пользователь в любой момент может проверить синтаксис или воспользоваться уже готовыми конструкциями (рис. 2). Рисунок 1. Структура проекта с программируемой логикой

Рисунок 2. Выбор готовых конструкций VHDL-описаний

Если схема проектируемого устройства была нарисована с использованием библиотечных примитивов, с помощью команды Properties к ней могут быть добавлены специфические свойства устройств фирмы-изготовителя. При запуске процесса функционального моделирования программа OrCAD Capture выполняет компилирование библиотек от производителя и установку параметров. Компиляция библиотек производится только один раз, при последующих запусках е╦ выполнять не нужно. Функциональное моделированиеНа этом этапе проектирования производится отладка проекта на обнаружение ошибок в проектируемой логике без временных расч╦тов. Для инициализации функционального моделирования используются ресурсы, размещ╦нные в папке администратора проекта. При необходимости, для моделирования проекта могут быть использованы средства внешней программы NC VHDL Desktop. В процессе функционального моделирования генерируются сигналы, подаваемые на входы проекта, и рассчитываются выходные сигналы, которые пользователь может сравнить с ожидаемыми результатами. Если результаты расч╦та не соответствуют ожидаемым, пользователь возвращается к редактированию проекта. При необходимости, имеется возможность создания и включения в проект контрольных тестовых файлов для проверки модели TESTBENCH. Запуск функционального моделирования осуществляется командой Simulate Preroute из меню Picflow. При работе с программой NC VHDL Desktop имеется возможность использовать интерактивный или пакетный режим для работы. Интерактивный режим позволяет взаимодействовать с модулем NC VHDL Desktop "на лету", в то время как пакетный режим вызывает его, чтобы запустить в фоновом режиме и выполнять моделирование в соответствии с указанными в существующем пакетном файле командами. Система позволяет управлять процессом моделирования и передавать в программу NC VHDL Desktop специальные опции. Например, включить отображение процесса моделирования на дисплее с помощью опции Start Sim Vision (рис. 3) или запустить интерактивный режим с помощью опции Enter Interactive Mode. Все данные, полученные в результате функционального моделирования, сохранятся в папке PIC Resource в подпапке Preroute. Рисунок 3. Просмотр результатов функционального моделирования

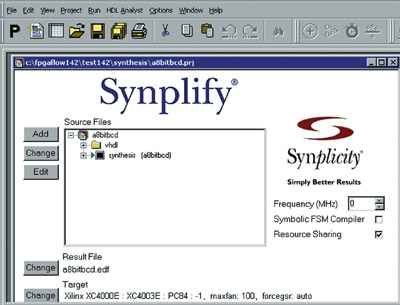

Синтез, размещение и трассировкаНа данном этапе для проекта генерируется список соединений в формате EDIF, который переда╦тся во внешнюю программу синтеза логики Synplify компании Synplicity (www.synplicity.com). Полученный список соединений содержит всю необходимую информацию для средств размещения и трассировки ПЛИС, генерирующих материальную модель проекта, которая может быть использована для моделирования задержек (рис. 4). Рисунок 4. Окно программы Synplify

Данная модель имеет иерархическую структуру и базируется на примитивных моделях, представленных в поставляемых производителем VHDL-библиотеках. При этом проект оптимизируется и из проекта удаляется избыточная логика. Моделирование задержекВременное моделирование позволяет рассчитать задержки в сигнальных трактах и убедиться, что временные характеристики поставляемых производителем микросхем не изменяют функционирования проекта. То есть, на данном этапе оценивается, что задержки распространения сигналов и некоторые другие параметры, например, форма фронтов сигнала, находятся в рамках допустимых пределов и не затрагивают логику проекта. Временные данные подключаются к проекту во время процесса размещения и трассировки (place and route) и имеют форму стандартного файла синхронизации (SDF) или аннотированного списка соединений. Для расч╦та задержек могут быть использованы входные сигналы, созданные на этапе функционального моделирования проекта с помощью средств NC VHDL Desktop. На этом этапе моделирования обнаруживается любое нарушение временных параметров, произошедшее в результате неправильной трассировки или логической реализации проекта. При обнаружении нарушений пользователь может вернуться на этап проектирования, чтобы найти более оптимальное решение или выполнить другую логическую реализацию. Ресурсы для этого вида моделирования сохраняются в папке Timer. Генерация элементаКак только результаты анализа будут полностью удовлетворять пользователя и будет получен конечный список соединений, с помощью функции Generate Part может быть сформирован элемент для последовательного использования в других проектах, в том числе, и для разработки печатной платы. Этот элемент представляет собой законченный FPGA/CPLD элемент, который является результатом процесса проектирования программируемой логики, который может быть включен в другой проект как самостоятельный компонент. При создании элемента программа OrCAD Capture созда╦т новую библиотеку и элемент с выводами, назначенными согласно спискам, представленным производителем микросхемы. Файлы "распиновки" для микросхем Actel, Vanits, Lattice, Xilinx включают номера выводов, имена сигналов и режим упаковки программируемых контактов в процессе размещения и трассировки. Контакты сортируются по именам в алфавитном порядке, входные контакты располагаются с левой стороны, выходные или двунаправленные - с правой стороны. Функция Generate Part может создавать новые элементы или обновлять номера контактов уже существующих библиотечных элементов, используя опцию UPDATE pins on existing part in library, которая разрешает при техническом проектировании проекта программируемой логики обновлять символы элементов. По умолчанию, созда╦тся элемент с количеством контактов, равным количеству входных и выходных портов в таблице соединений. Созданному элементу может быть присвоен определ╦нный тип, определяющий его иерархию при системном моделировании. Это может быть:

Вы можете использовать сгенерированный элемент как библиотечный в схемах для других проектов, включая PCB-проект. |

||||||||||||||||||||||||||||||||||||||||||

Новые возможности OrCAD 10.0

Новые возможности OrCAD 10.0