ПОСЛЕДОВАТЕЛЬНОСТЬ ВКЛЮЧЕНИЯ ИСТОЧНИКОВ ПИТАНИЯ В СИСТЕМАХ С НЕСКОЛЬКИМИ ПИТАЮЩИМИ НАПРЯЖЕНИЯМИ

От редакции

Предлагаемый вниманию читателей материалу открывающий новую рубрику «Библиотечка разработчика»у был представлен специалистами компании Texas Instruments в рамках проведенного ими в апреле этого года в Москве семинара по источникам питания.

Он предназначен широкому кругу разработчиков современных систем обработки сигнала.

СОДЕРЖАНИЕ

При разработке систем с несколькими питающими на-пряже ниями разработ ч икам следует учитывать различные скорости нарастания и спада питающих напряжений при их включении и выключении. Простой пример такой системы — цифровой сигнальный процессор (DSP) с различными питающими напряжениями для ядра и портов ввода-вывода, что требует корректной последователmности включения источников питания. Пренебрежение этими вопросами может привести к выходу устройства из строя под воздействием тиристорного эффекта а также к появлению значительных токовых перегрузок. Тиристорный эффект может возникнуть при наличии различных потенциалов у ядра и интерфейса портов ввода-вывода. В этой статье описаны некоторые общие требования к правильной последовательности включения источников питания для цифровых сигнальных процессоров (DSP), и рограммиpуемых логических интегральных схем (FPGA), специализированных интегральных микросхем (ASIC) и микропроцессоров, рассмотрен ряд практических решений с использованием специальных устройств контроля питания — секвенсеров. В схемах секвенсеров используются преимущества дополнительных выводов сброса (reset), установления выхода (power good), разрешения (enable) и плавного запуска (soft-start) имеющихся у различных устройств контроля питания, начиная от регуляторов с низким падением на проходном элементе (LDO) и заканчивая специализированными встраиваемыми модулями питания.

I. ВВЕДЕНИЕ

Высокопроизводительные устройства обработки сигналов, такие как FPGA, ASIC, PLD и DSP, зачастую требуют нескольких источников питания, раздельных для ядра и портов ввода-вывода. Порядок, в котором данные источники питания должны включаться и выключаться, исключительно важен для долговременной бесперебойной работы устройства. В данной статье обосновывается необходимость корректной последовательности включения источников питания и даются практические рекомендации по реализации такой последовательности.

II. ДЛЯ ЧЕГО НУЖНА ОПРЕДЕЛЕННАЯ ПОСЛЕДОВАТЕЛЬНОСТЬ ВКЛЮЧЕНИЯ ИСТОЧНИКОВ ПИТАНИЯ?

Системы, разработанные без учета корректной последовательности включения источников питания, подвержены потенциальным рискам, включая снижение надежности и повышенную вероятность выхода из строя. Снижение надежности происходит за счет того, что устройствам с несколькими питающими напряжениями приходится в течение продолжительного времени работать в технически недопустимых условиях. Одной из таких опасных ситуаций является пропадание одного из питающих напряжений на длительное время. При этом могут выйти из строя цепи защиты от статического напряжения (ESD) и другие внутренние элементы схемы, связывающие узлы, запитываемые разными источниками питания. Период времени, в течение которого устройство может работать в таких условиях до выхода из строя, может быть достаточно большим и измеряться месяцами, однако, любое подобное воздействие негативно влияет на срок службы устройства. Конечно, несколько некорректных включений и выключений навряд ли приведут к выходу устройства из строя, но часто включаемые устройства имеют большую вероятность аварии именно по этой причине.

Еще один аспект неверной последовательности включения источников питания может привести к немедленному выходу устройства из строя. Речь идет о значительном превышении допустимого тока через выводы либо превышении допустимой разницы потенциалов, что приводит к повреждению внутренних элементов схемы, аналогичному описанным выше. Разница заключается лишь в различном воздействии данных факторов на устройство.

А. Тиристорный эффект

Ввиду того, что подавляющее большинство устройств с несколькими источниками питающего напряжения выполнены по КМОП-технологии, в них происходят повреждения, носящие название тиристорного защелкивания. Такой эффект может возникать при воздействии на включенное устройство напряжений или токов недопустимых величин. Внешнее проявление тиристорного эффекта выражается в значительном повышении потребляемого устройством тока, при этом устройство может временно потерять работоспособность либо вовсе выйти из строя.

|

|

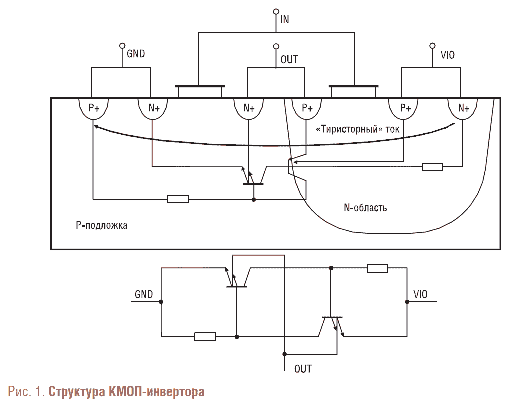

На рис. 1 изображена внутренняя структура КМОП — инвертера и образуемые в ней паразитные биполярные транзисторы. Сток N-канально-го МОП-транзистора служит эмиттером, N-область образует коллектор, а Р-подложка служит базой паразитного биполярного N-P-N транзистора. Аналогично, сток Р-канально-го МОП-транзистора работает как эмиттер, N-область образует базу, а подложка служит коллектором паразитного биполярного P-N-P транзистора. Эти два паразитных транзистора формируют PNPN структуру, известную как тиристор (SCR). В нормальном состоянии PN-переходы паразитных транзисторов являются обратносмещенными. Тем не менее, при определенных условиях, возникающих при переходных электрических процессах, PN-переход паразитного тиристора может оказаться прямое мещенным, что приводит к открытию тиристора и возможному повреждению устройства. К такому эффекту могут привести различные процессы, включающие превышение напряжением на выводах питающих напряжений, токовые перегрузки в подложке или N-области, а также токи смещения в подложке или N области, возникающие при быстрых переходных процессах во внутренних структурах.

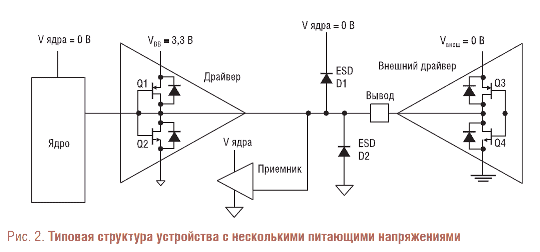

На рис. 2 приведена типовая структура устройства с несколькими питающими напряжениями, такого, как, например, программируемая ло-гическ а я микросхема (Р L D ), подключенного к внешнему драйверу. Для иллюстрации проблем, возникающих при последовательном подключении источников питания, рассмотрим систему, состоящую из трех источников питания: V ядра, V вв и Vвнеш с уровнями в 5 В; 3,3 В и 3,3 В соответственно. Рассмотрим следующий сценарий: источник Vвв включен, Vядра выключен, выход драйвера не инициализирован. Таким образом, выход драйвера находится в неизвестном состоянии, Q1 может быть прямосмещенным и проводить ток через защитный диод. Величина тока зависит от импеданса Ql, D1 и отключенного источника питания. Тиристорный эффект может возникнуть, если во время протекания тока через защитный диод будет подано питание ядра. К каким последствиям этот эффект приведет — немедленному выходу из строя, снижению долговременной надежности либо вообще не нанесет вреда — зависит исключительно от корректной разработки устройства. Другими словами, устройству не будет причинен вред только в том случае, если величина протекающего тока значительно ниже опасного для кремния уровня.

Вероятность возникновения тиристорного эффекта возрастает в том случае, когда различные периферийные устройства, такие, как, например, преобразователи данных и микросхемы памяти, запитан-ные от различных источников, объединяются своими выводами на портах ввода-вывода устройства с несколькими питающими напряжениями. На рис. 2 показан пример ситуации, когда внешний драйвер, подключенный к порту ввода-вывода, имеет цепь «подпитки» через паразитный антипараллельный диод транзистора Q3, когда напряжение Увнеш меньше, чем Увв.

Такая ситуация может с легкостью быть исправлена присоединением VBвнеш и Vвв к одному источнику питания. Другая, опасная в плане возникновения тиристорного эффекта, ситуация может возникнуть в том случае, когда возникают броски напряжения Vвв или Vядра, когда Vвнеш подключено и ток от внешнего драйвера течет через вход.

Тенденции в современной полупроводниковой промышленности включают в себя постоянное повышение быстродействия, добавление дополнительных функций, снижение энергопотребления и размеров устройств одновременно с уменьшением времени разработки. Для достижения этих целей разработчики микросхем стараются «уплотнять» структуру кристаллов, используя для этого более «тонкие» технологические нормы и повышая концентрацию компонентов на единицу площади. К сожалению, при этом увеличивается омическое сопротивление и коэффициент усиления по току («бета») паразитных PNP и NPN транзисторов, что, в свою очередь, повышает вероятность возникновения тиристорного эффекта. С целью борьбы с данным эффектом используются специальные защитные цепи и «охранные кольца». Защитные цепи используются на входах и выходах для безопасного отвода токов, а охранные кольца позволяют снизить сопротивление. К сожалению, необходимость применения таких мер является обратной стороной уменьшения размера и цены устройств.

Такие параметры, как напряжение питания ядра, восприимчивость к тиристорному защелкиванию и последовательность подачи питающих напряжений, зачастую определяются уже только после выпуска и тестирования пилотной партии кристаллов. С учетом требований минимальной стоимости и времени выхода новой продукции на рынок, если в процессе тестирования выявлены лишь некоторые особенности (такие, например, как предпочтительный порядок подачи питающих напряжений), эти особенности документируются, а изделие передается в серийный выпуск.

В. Конфликт шин на системном уровне

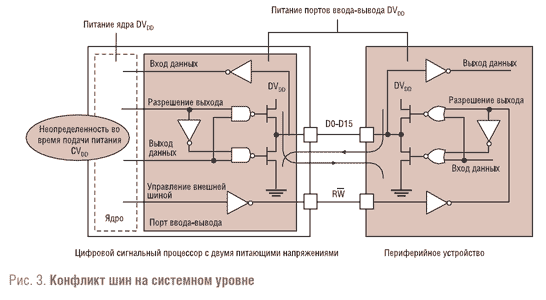

Правильная последовательность подачи питающих напряжений зачастую позволяет избежать состояния, называемого конфликтом шин на системном уровне, в котором двунаправленные порты ввода-вывода цифрового сигнального процессора и внешних периферийных устройств конфликтуют друг с другом. Так как логика управления шиной находится в той же части кристалла ЦСП, что и ядро, подача питания на порты ввода-вывода прежде, чем на ядро может привести к тому, что и выводы ЦСП и выводы внешнего устройства будут одновременно сконфигурированы как выходы. Если данные на шине с разных сторон не идентичны, это приведет к конфликту выходных драйверов устройств, как показано на рис. 3.

По одному из изображенных путей (в зависимости от установившихся данных на шинах) потечет ток в том случае, когда данные с двух сторон различны. Этот ток может быть столь значительным, что приведет к повреждению двунаправленных выходных портов. Для избегания такой ситуации следует выполнять рекомендации по запитке ядра процессора одновременно (либо раньше) с портами ввода-вывода, что позволит предотвратить неопределенное состояние сигналов на шине.

III. СХЕМЫ ПОДАЧИ ПИТАНИЯ

Существует три основных типа схем подачи и снятия питания в системах с несколькими источниками: последовательная, зависимая и одновременная [5]. Выбор подходящей схемы зависит от требований к устройству. В документации производителей, как правило, отсутствуют четкие указания по применению той или иной схемы подачи питающих напряжений, вместо этого указываются предельно допустимые амплитудные и временные параметры напряжений на выводах питания. Следует учитывать, что некоторые устройства выходят из строя даже при очень непродолжительном превышении максимально допустимых параметров. Использование таблиц и графиков максимально допустимых параметров зачастую позволяет выбрать оптимальную методику подачи питающих напряжений, удовлетворяющую приведенным требованиям.

А. Последовательная схема

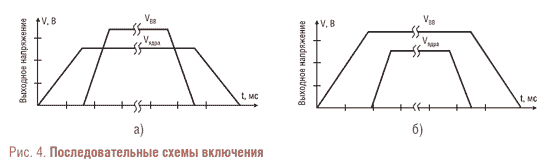

Последовательная схема включения работает следующим образом. После включения одного из источников питания, нарастания его выходного напряжения до стабилизированного значения и выдержки определенной паузы включается второй источник. Этот метод позволяет инициализировать определенные части схемы с целью придания им фиксированного состояния перед активизацией следующего питающего напряжения. Примером может служить подача питания ядра перед запиткой портов ввода-вывода, как изображено на рис. 4а.

Ниже приведена выдержка из спецификации на микросхему с рекомендациями, определяющими выбор последовательной схемы включения:

«Системные особенности, такие, как конфликт шин, могут потребовать применения специальных схем подачи питающего напряжения. В таком случае, питание ядра должно быть подано одновременно или раньше питания буферов ввода-вывода, а снято после обесточивания портов ввода-вывода.»

Другим возможным вариантом последовательной схемы является подача питания на порты ввода-вывода прежде, чем на ядро, которое затаптывается только после достижения питающим напряжением портов уровня стабилизации, как изображено на Рис. 4б. В конкретном примере, должен применяться именно такой метод с целью выполнения рекомендаций производителя по подаче питающих напряжений с учетом того, что задержка подачи питания ядра не должна превышать 100 мс. Как будет показано далее, стандартная аппаратная реализация такого метода заключается в использовании встроенного в Стабилизатор монитора питания с подключением его вывода установления выхода power good (PG) ко входу разрешения enable (EN) второго источника питания.

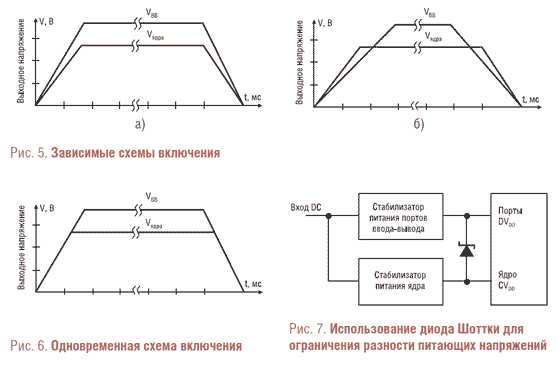

В. Зависимая схема

Особенность зависимой схемы заключается в том, что оба источника включаются одновременно и скорость нарастания их выходного напряжения одинакова вплоть до достижения уровня стабилизации. На рис. 5а изображена работа зависимой схемы подачи питающих напряжений. Как видно из рисунка, напряжение питания портов ввода-выво-да и напряжение питания ядра достигают уровня стабилизации приблизительно одновременно. Во время нарастания напряжения после включения пропорция между двумя источниками сохраняется. Проще говоря, питающее напряжение ядра всегда составляет определенный процент от питающего напряжения портов. В другом варианте зависимой схемы, представлен¬ном на рис. 56, напряжение питания ядра нарастает и спадает несколько быстрее, чем напряжение питания портов ввода-вывода. В таком случае, для предотвращения конфликта на шине ядро запитывается несколько раньше, чем порты, при этом гарантируется корректная инициализация последних.

С. Одновременная схема

Одновременная схема подачи питающих напряжений аналогична зависимой схеме в том плане, что нарастание обоих напряжений происходит одновременно. Отличие заключается в том, что задачей одновременной схемы является снижение разности между двумя питающими напряжениями во время нарастания и спада, как показано на рис. 6, до тех пор, пока напряжение питания ядра не достигнет уровня стабилизации. Этот метод обычно используется в тех случаях, когда существуют цепи утечек между шинами питания либо когда неопределенность внутренней логики приводит к значительному повышению пусковых токов. В документе [9] рекомендуется применять одновременную схему для снижения пусковых токов.

Ниже мы рассмотрим несколько примеров реализации секвенсеров с использованием различной элементной базы:

• Диодов

• Регуляторов с низким падением на проходном элементе (LDO)

• Супервизоров (SVS)

• Ключей питания

• Контроллеров «горячего» включения (Hot-swap)

• Микроконтроллеров

• Контроллеров импульсных блоков питания (с вне¬шним МОП-ключом)

• Импульсных преобразователей (с встроенным МОП- ключом)

• Готовых встраиваемых модулей питания

IV. РЕАЛИЗАЦИЯ СЕКВЕНСЕРОВ ПИТАНИЯ НА БАЗЕ РЕГУЛЯТОРОВ С НИЗКИМ ПАДЕНИЕМ НА ПРОХОДНОМ ЭЛЕМЕНТЕ (LDO)

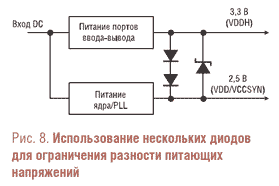

А. Диоды

Диоды имеют широкое использование в цепях секвенсеров питания. Несмотря на то, что только с их помощью невозможно реализовать ни последовательную, ни зависимую, ни одновременную схему включения в чистом виде, диоды помогают соблюдать требуемые соотношения между питающими напряжениями. На рис. 7 показан пример использования диода Шоттки для ограничения разницы между напряжениями питания ядра и портов ввода-вывода. Такое решение позволяет уменьшить потенциальное негативное воздействие на устройство «привязкой» уровня питания портов ввода-вывода и уменьшением задержки между нарастанием питающего напряжения на разных шинах.

На рис. 8 показана схема, представляющая собой комбинацию из нескольких диодов и позволяющая реализовать следующие требования к питанию микроконтроллеров:

• VIN никогда не должно превышать VDDH на более, чем 2, 5 В, в том числе во вре¬мя сброса по включению питания

• VDDH никогда не долж¬но превышать VDD/VCCSYN на более, чем 1,6 В, в том числе во время сброса по включению питания.

• VDD/VCCSYN никогда не должно превышать VDDH на более, чем 0,4 В, в том числе во время сброса по включению питания.

Примечание: Микросхема содержит встроенные встречно включенные диоды между

выводами VDDH и VDD, для защиты от электростатики (ESD).

Если одно из питаний (VDD или VDDH) подано, а второе

отсутствует, то отсутствующее питание будет подано через встроенный диод.

Проблемы могут возникнуть в том случае, если одно из питаний подано

(VDD или VDDH), а вывод второго питания замкнут на

«землю» (GND). В этом случае существует опасность выхода из строя

внутренних защитных диодов.

Для получения реальных последовательных, одновременных и зависимых схем секвенсеров следует использовать активные компоненты, такие схемы мы рассмотрим ниже.

В-Управление входом разрешения (Enable) регуляторов с низким падением на проходном элементе (LDO) при помощи супервизоров (SVS)

Реализация последовательной схемы:

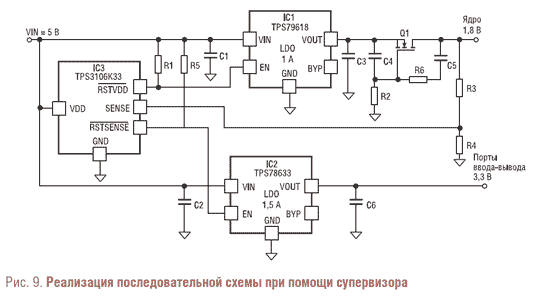

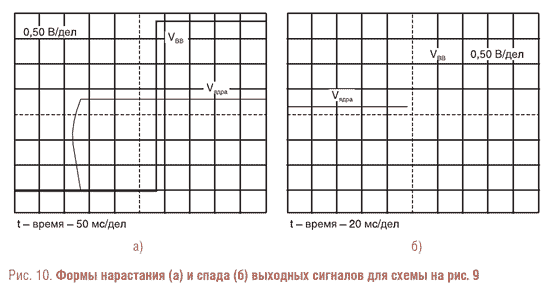

На рис. 9 показан пример использования супервизора (SVS) для реализации последовательной схемы секвенсирования. Нагрузкой источника питания служит программируемая логическая интегральная схема (FPGA), для которой, требуется последовательная схема включения источников питания. В показанном решении используется 5-вольтовая шина питания. В первую очередь запитывается ядро, а после достижения питающим напряжением требуемого значения разрешается включение питания портов ввода-вывода. Преимущества линейного Стабилизатора по сравнению с импульсным, как правило, заключаются в пониженном уровне пульсаций на выходе, снижении места, занимаемого на плате и более низкой цене. Основной недостаток - более низкий КПД и, за счет этого, более высокая рассеиваемая мощность.

В этом схемотехническом решении использованы две микросхемы регуляторов с низким падением на проходном элементе (LDO), IC1 для питания ядра и IC2 для питания портов ввода-вывода совместно с супервизором IC3. Сдвоенный супервизор с порогом 2,941 В (типовое значение) контролирует входное питание. Как только напряжение на входе превысит пороговое значение 2,941 В, выход сброса супервизора перейдет из состояния логического нуля в высокоимпедансное состояние после задержки в 130 мс, включая при этом выход микросхемы LDO IC1. После этого напряжение ядра на выходе LDO IC1 начинает расти вплоть до значения в 1,8 В. Для защиты входного напряжения от просадки под воздействием высоких пусковых токов FPGA и тока заряда конденсаторов в схему включен ограничитель тока. В противном случае возможна ситуация, когда входное напряжение упадет ниже пороговой величины в процессе включения. Цепь ограничения тока, включающая в себя Q1, С4, R2, R6 и С5, обеспечивает плавный заряд и включение нагрузки.

Напряжение питания ядра контролируется Компаратором, встроенным в супервизор IC3. Резистивный делитель R3/R4 устанавливает напряжение срабатывания на необходимом в конкретном случае уровне, в данном случае порог устанавливается на уровне 1,7 В. По достижении напряжением ядра порога, IC3 разрешает выход микросхемы LDO IC2, питающей порты ввода-вывода системы, при этом напряжение питания портов нарастает до значения 3,3 В.

Формы нарастания и спада выходных сигналов для этой схемы приведены на рис. 10.

Реализация одновременной схемы:

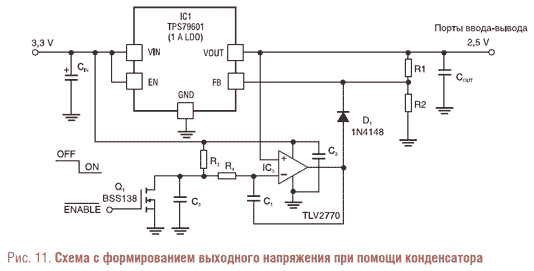

В некоторых случаях требуется определенная скорость нарастания питающего напряжения, либо ограничение пускового тока. В таких случаях можно использовать схему на рис. 11.

Система контроля включения-выключения использует цепь R3 — С2 для формирования требуемой формы нарастания и спада напряжения. Этой цепью задается скорость изменения напряжения на выходе LDO во время включения и выключения. Операционный усилитель сравнивает выходное напряжение, поступающее на его неинвертирующий вход с опорным напряжением, поступающим на инвертирующий вход. При этом он подстраивает выходное напряжение таким образом, что его скорость нарастания определяется RC цепью. Когда на входе разрешения ENABLE низкий уровень, транзистор Q1 закрыт и конденсатор С2 заряжается через резистор R3 до уровня входного напряжения. После того, как выходное напряжение VOUT достигает значения 2,5 В, устанавливаемого делителем R1/ R2, напряжение на инвертирующем входе операционного усилителя продолжает расти, что приводит к снижению напряжения на выходе ОУ. Диод D1 при этом переходит в обрат-носмещенное состояние, а цепь контроля нарастания и спада напряжения далее не участвует в обратной связи стабилизатора. R4 и С1 обеспечивают плавное нарастание напряжения при включении.

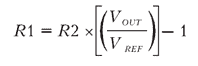

Выходное напряжение для данного примера вычисляется следующим образом:

где VREF = 1,224 В для указанного на схеме типа LDO

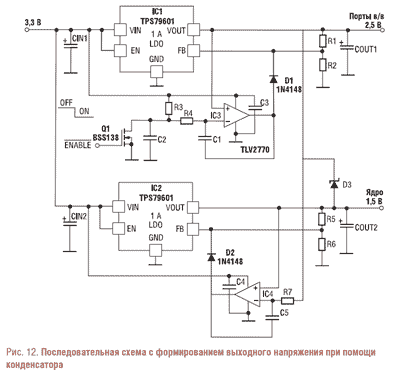

На рис. 12 показана реализация одновременной схемы, осуществляющей формирование требуемой формы нарастания и спада напряжения и использующей IC2 в качестве следящего стабилизатора LDO.

Система формирования требуемой формы нарастания и спада напряжения аналогична описанной в предыдущем примере. Отличие заключается в том, что напряжение питания ядра в данном случае управляет напряжением питания портов ввода-вывода. Кроме этого, напряжение питания портов не должно отличаться более, чем на 600 мВ от напряжения питания ядра во время включения и выключения, в противном случае возможно повреждение кристалла из-за открытия диода подложки.

Во время включения и выключения микросхема IC4 осуществляет слежение, обеспечивая разность между напряжениями питания ядра и портов ввода-вывода на уровне, существенно меньшем допустимых 600 мВ. Диод Шоттки D3 является дополнительной степенью защиты.

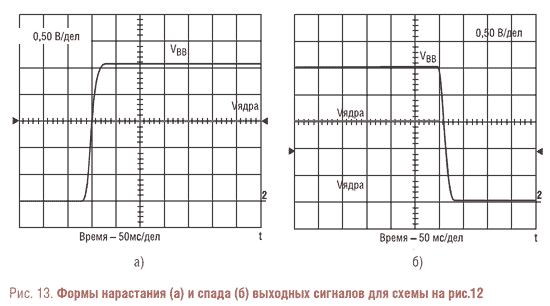

Во время включения напряжение на выходе микросхемы IC1 нарастает в соответствии с формой сигнала на инвертирующем входе О У IC3. Операционный усилитель IC4 обеспечивает формирование сигналов нарастания и спада, получая информацию с цепи питания 2,5 В портов ввода-вывода. Во время включения напряжение питания портов медленно нарастает, и это напряжение поступает на инвертирующий вход микросхемы IC4. Неинвертирующий вход контролирует напряжение питания ядра, которое поступает с выхода линейного стабилизатора IC2. После того, как напряжение питания ядра достигает значения 1,5 В, устанавливаемого делителем R5/R6, напряжение на инвертирующем входе операционного усилителя IC4 продолжает расти, что приводит к снижению напряжения на выходе ОУ. Диод D2 при этом переходит в обратносмещен-ное состояние, а цепь контроля нарастания и спада напряжения далее не участвует в обратной связи стабилизатора. На рис. 13 показаны формы нарастания и спада выходных сигналов для этой схемы.

С. Использование регуляторов с низким падением на проходном элементе (LDO) и ключей управления питанием

Реализация последовательной схемы:

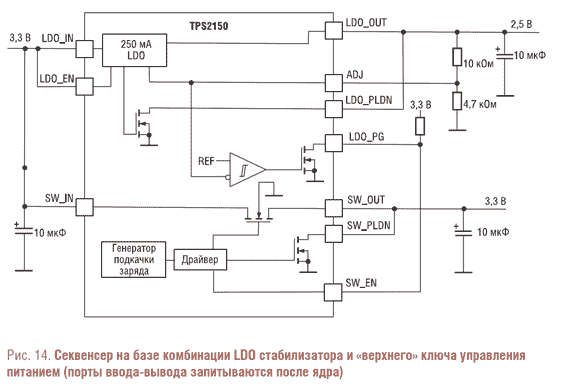

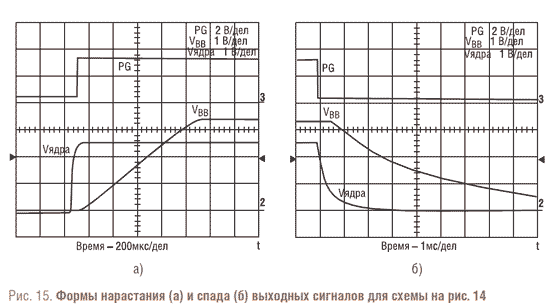

В некоторых случаях разработчику требуется обеспечить подачу напряжения питания ядра до того, как подано питание портов ввода-вывода, даже если напряжение источника питания уже достигло уровня, требуемого для портов ввода-вывода. Для того, чтобы обеспечить отключение источника питания портов ввода-вывода до тех пор, пока не стабилизируется напряжение питания ядра, удобно использовать «верхние» ключи управления питанием. На рис. 14 показана реализация последовательной схемы с использованием микросхемы TPS2150, содержащей «верхний» ключ питания и LDO-регулятор. TPS2150 использует выход установления питания «power good» стабилизатора LDO для управления ключом питания. Результирующие осциллограммы при включении изображены на рис. 15а. Также в схеме имеется ключ на «землю» на МОП-транзисторе для разряда выходных емкостей при принудительном отключении устройства (рис. 156).

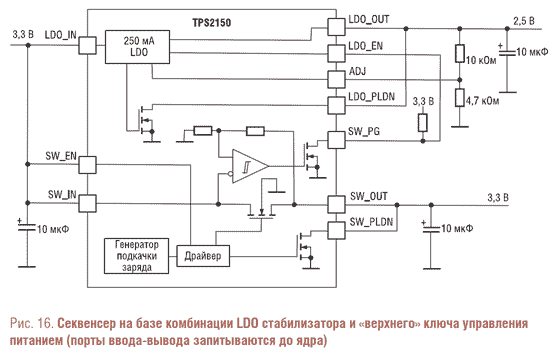

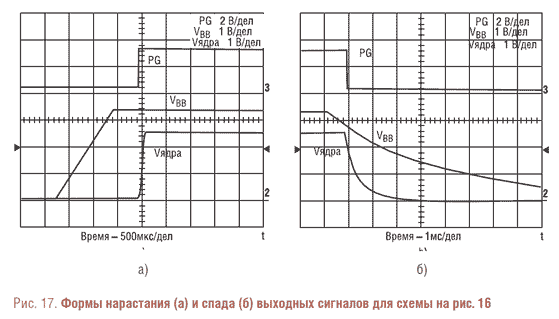

На рис. 16 показана альтернативная конфигурация, в которой питание портов ввода-вывода при включении подается прежде питания ядра. Соответствующие осциллограммы приведены на рис. 17

D. Контроллеры «горячего» подключения (Hot-Swap)

Реализация одновременной схемы:

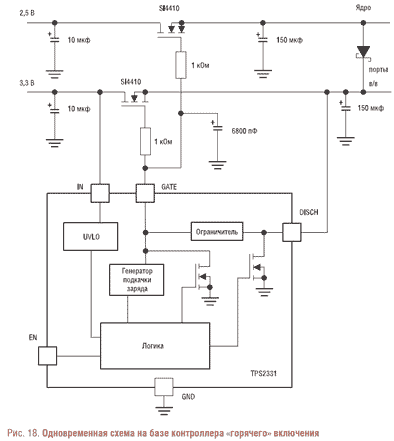

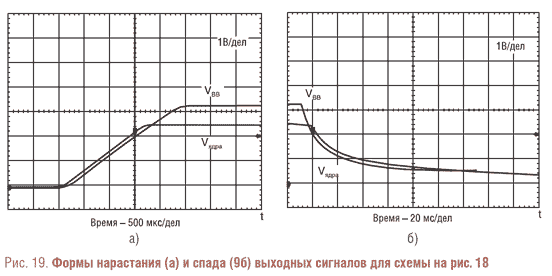

Другим способом подачи и снятия питания с сохранением минимальной разности между шинами питания является использование полевых МОП-транзисторов(MOSFET) между шинами питания и нагрузкой. На рис. 18 показана упрощенная схема с использованием двух MOSFET и контроллера «горячего» подключения TPS2331, реализующая одновременное включение. Так как затворы обоих транзисторов управляются одним и тем же драйвером, нарастание питания на шинах происходит почти одновременно (рис. 19а). Контроллер TPS233I имеет также встроенный ключ на «землю» для разряда выходных конденсаторов при выключении, см. рис. 196. Диод Шот-тки шунтирует шину питании ядра при выключении.

Продолжение следует.

Журнал "Новости Электроники", номер 2, 2005 год

Журнал "Новости Электроники", номер 2, 2005 год