Подключение сигнальных цепей в мощных преобразовательных устройствах

В статье даются рекомендации по трассировке цепей управления, соединяющих контроллер, драйвер и выводы IGBT. Следование этим несложным правилам поможет разработчикам решить ряд основных вопросов, возникающих при проектировании силовых преобразователей.

Данная статья заканчивает цикл материалов [1], посвященных проблемам управления изолированным затвором MOSFET/IGBT. В предыдущих публикациях мы рассматривали методики расчета режимов работы драйвера и выбора элементов затворной цепи.

Соединение контроллера и драйвера

При разработке топологии подключения сигнальных входов схем управления затворами основное внимание должно быть уделено обеспечению помехозащищенности. Существует достаточно много причин возникновения электромагнитных помех, способных вызвать фатальные искажения контрольных сигналов. Главным источником шумов является процесс коммутации IGBT и образующиеся при этом скоростные фронты токов и напряжений (di/dt, dv/dt). На практике именно помехи, наводимые со стороны выходных цепей инверторов, могут достигать логических уровней драйверов и приводить к ложным срабатываниям. Отсюда вытекает первое требование к конструкции силового преобразовательного устройства: силовые и сигнальные кабели должны располагаться как можно дальше друг от друга.

Существует несколько стандартных рекомендаций, выполнение которых позволяет свести к минимуму негативное влияние фронтов напряжений на цепи, соединяющие контроллер и драйвер:

- сигнальные линии на печатных платах должны иметь минимально возможную длину, петлевые связи должны быть полностью исключены;

- соединительные шлейфы должны иметь минимально возможную длину (не более 3 м), желательно выполнять все связи витыми парами;

- не следует объединять сигнальные провода в общий жгут с мощными кабелями (питание и выходы), а также прокладывать их вблизи силовых терминалов, заземляющих проводов и конденсаторов DC-шины. Расстояние между сигнальными и мощными цепями должно быть не менее 30 см, трассировка кабелей должна обеспечивать их перпендикулярное расположение. Рекомендуется прокладывать жгуты вблизи заземленных частей конструкции (радиатор, рама);

- заземление и сигнальных и силовых цепей следует выполнять раздельно, точка их соединения в большинстве случаев располагается вблизи драйвера, что позволяет избежать образования контурных токов;

- в устройствах, характеризующихся высоким уровнем шумов, рекомендуется использовать экранированные сигнальные кабели или ВОЛС (волоконно-оптические линии связи);

- для повышения коэффициента подавления дифференциальных помех рекомендуется установка небольшого конденсатора (несколько нФ) между цепями силовой и сигнальной земли на входе драйвера.

На рисунке 1 схематично показано соединение сигнальных выводов схемы управления затворами.

Рис. 1. Соединение цепей контроллера и драйвера

Емкость 1 нФ, подключенная ко входу драйвера, предназначена для повышения уровня его помехозащищенности. Необходимо отметить, что при использовании контроллера совместно с буферным линейным усилителем, обеспечивающим ограничение тока, этот конденсатор вносит небольшую задержку (несколько нс).

Соединение драйвера и модуля IGBT

Залогом надежной работы силового преобразовательного устройства является корректное подключение входов силовых ключей. Для уменьшения влияния распределенной индуктивности линий связи схема управления затворами должна располагаться максимально близко к модулю IGBT. В ряде случаев, например, при управлении параллельным соединением ключей, выполнение этого требования затруднено. Если расстояние между драйвером и входами силового ключа превышает 5 см, соединение должно быть выполнено витой парой.

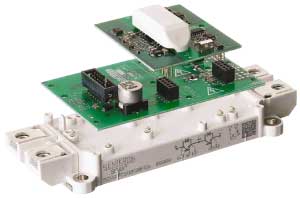

Оптимальным решением, особенно для преобразователей высокой мощности, является размещение драйвера непосредственно на корпусе IGBT. Такую возможность предоставляют новые конструктивы силовых модулей, к которым относятся, например ключи SEMiX и SKiiP, имеющие разнесенные по разным сторонам корпуса DC- и AC-терминалы.

Примером очень удачной конструкции, обеспечивающей высокую степень стойкости к наведенным помехам, является сборка SEMiX / SKYPER 32, показанная на рисунке 2 [3].

Рис. 2. Драйвер SKYPER 32 монтируется непосредственно на модуль IGBT SEMiX

Универсальное устройство управления изолированными затворами SKYPER 32 может сопрягаться с модулями различных типов с помощью интерфейсных плат, что обеспечивает высокую гибкость и масштабируемость. При сопряжении модуля, драйвера и переходной платы все электрические связи обеспечиваются только за счет прижима, паяные соединения полностью исключены. Спиральные пружинные контакты SEMiX, соединяющие входы управления IGBT с выходами драйвера, расположены в непосредственной близости от силовых чипов. Это позволяет обеспечить не только минимальную длину сигнальных связей, но и высокую стойкость к механическим воздействиям, а также отсутствие усталостных процессов пайки. Подобные сборки могут рассматриваться как интеллектуальные силовые модули (IPM), предназначенные для работы в диапазоне мощностей от десятков до сотен кВт.

Как и в предыдущем случае, существует ряд стандартных рекомендаций, выполнение которых позволяет повысить помехозащищенность линий управления затворами:

- конструкция DC-шины должна обеспечивать низкие потери проводимости и минимальное значение распределенной индуктивности для снижения уровня переходных перенапряжений. С этой же целью рекомендуется применение емкостных снабберов между терминалами питания модулей;

- соединения выходов драйвера с выводами затвора и эмиттера IGBT должны иметь минимальную длину и выполняться витой парой для компенсации взаимной индукции. Объединение в одном жгуте проводов затворных цепей модулей, расположенных в разных плечах/фазах, недопустимо (образец соединения выходных цепей дрвйвера показан на рисунке 3);

- линии мониторинга напряжения насыщения (VCEsat) схемы защиты DESAT должны прокладываться отдельно от выводов управления IGBT;

- рекомендуется установка резистора утечки в цепи «затвор - эмиттер» RGE (10...50 кОм) вблизи IGBT;

- для ограничения напряжения VGE целесообразно использовать диод-супрессор, который должен быть размещен в непосредственной близости от IGBT;

- использование силового терминала эмиттера для подключения вывода управления недопустимо. Напряжение, наводимое при коммутации на паразитной индуктивности эмиттерной цепи LES, может изменить уровень сигнала управления VGE и вызвать ложное срабатывание;

- в ряде случаев, особенно в применениях высокой мощности, рекомендуется устанавливать конденсатор СGE параллельно выводам управления в непосредственной близости от силового ключа, номинал СGE должен составлять примерно 10% от входной емкости IGBT;

- резисторы цепей включения и выключения затвора RGon/RGoff должны по возможности располагаться рядом.

Рис. 3. Соединение выходных цепей драйвера

Ограничение напряжения на затворе

Выход из строя силового ключа из-за повреждения изолированного затвора является достаточно распространенной неисправностью. Пробой цепи затвора может произойти вследствие банальных нарушений правил защиты от ESD (электростатического разряда), в результате возникновения колебаний в контуре, образованном индуктивностью цепи управления и емкостями затвора, а также из-за перенапряжения, наведенного со стороны схемы управления или силовых цепей вследствие емкостной или индуктивной связи.

В ряде случаев, особенно когда драйвер не может быть размещен в непосредственной близости от силового ключа, или он используется для управления несколькими параллельно соединенными модулями, следует применять дополнительные средства защиты затвора. Наиболее употребимые на практике схемы показаны на рисунке 4.

Рис. 4. Способы ограничения напряжения на затворе

Резистор RGE, установленный параллельно цепи «затвор - эмиттер» (см. рис. 4а), конечно не может ограничить напряжение VGE. Однако установка такого сопротивления рекомендуется рядом производителей (в том числе и SEMIKRON), его задачей является защита от статического электричества и предотвращение «перезаряда» входной емкости затвора при увеличении импеданса цепи управления.

Классическая схема ограничения напряжения VGE с помощью быстрого стабилитрона или супрессора (в англоязычной литературе TVS - Transient Voltage Suppressor) показана на рисунке 4б. Большим достоинством данной схемы является то, что при ее использовании удается снизить ток КЗ и уменьшить колебательность в режиме КЗ благодаря ограничению напряжения, наведенного на затвор через емкость Миллера (емкость «коллектор - затвор», CCG). Эту же задачу выполняет сглаживающий конденсатор CGE, наличие которого позволяет подавить паразитные генерации в цепи затвора при КЗ.

В ряде случаев хорошим решением является установка диода Шоттки между затвором и низковольтной цепью питания драйвера V+supply (рис. 4в). Использование такого способа ограничения напряжения VGE рекомендуется в том случае, если источник питания расположен в непосредственной близости от входа силового ключа (расстояние не более 5 см).

На рисунке 5 показана схема и внешний вид платы, осуществляющей согласование и защиту входов управления полумостового модуля IGBT.

Рис. 5. Схема и внешний вид платы согласования входов управления модуля IGBT (полумост)

Такая схема используется в большинстве конструкций, разработанных и производимых компанией SEMIKRON. На плате расположены раздельные для режимов включения и выключения резисторы затвора (RGon и RGoff), а также упомянутые выше резистор утечки RGE и диод-супрессор (TVS).

Параллельное соединение затворов

Параллельное соединение чипов и силовых модулей является основным способом наращивания мощности как самих электронных ключей, так и преобразователей на их основе. В современной силовой электронике это в первую очередь относится к транзисторам с изолированным управляющим затвором - MOSFET и IGBT. Даже одиночный кристалл состоит из множества параллельно соединенных ячеек, практически любой силовой ключ с достаточно высоким током коллектора содержит несколько параллельных чипов.

Невозможно до бесконечности увеличивать площадь кристалла или повышать плотность тока - при этом неизбежно сокращается выход годных изделий и становится невозможным эффективный отвод тепла с единицы площади. Разработчики силовых чипов постоянно совершенствуют технологии, стремясь к снижению потерь и увеличению допустимой токовой нагрузки. Однако все имеет свои физические ограничения, и на сегодняшний момент классические технологии производства MOSFET/IGBT близки к пределу возможностей по уменьшению потерь проводимости и переключения.

Параллельная работа ключей в импульсных режимах создает ряд проблем, главной из которых является необходимость статической и динамической токовой балансировки. К счастью, задачу выравнивания токов в состоянии проводимости можно считать решенной благодаря тому, что современные технологии производства кристаллов IGBT обеспечивают положительный температурный коэффициент напряжения насыщения VCEsat. Намного сложнее дело обстоит с антипараллельными диодами: только новейшие кристаллы серии CAL HD производства SEMIKRON имеют положительный тепловой коэффициент прямого напряжения VF при номинальных токах.

Основной трудностью параллельного соединения является невозможность производства чипов и модулей с полностью идентичными характеристиками. Источником проблем в динамических режимах является также неизбежная асимметрия линий подключения, приводящая к тому, что распределенные паразитные индуктивности в цепях коммутации тока параллельных модулей существенно отличаются. Такая разница в худшем случае может привести к критической перегрузке одного из кристаллов, что особенно сильно проявляется в наиболее напряженном динамическом режиме - коротком замыкании (КЗ).

В аварийных состояниях схема защиты производит отключение силовых транзисторов при токах, в 5...10 раз превышающих номинальные значения. Суммарное напряжение Vov = VDC + ∆V = VDC + LB × dIsc/dt (dIsc/dt - скорость отключения тока КЗ), воздействующее при этом на кристалл, может превысить напряжение пробоя. При параллельном включении топология силовых шин должна не только обеспечивать минимальное значение распределенных индуктивностей, но и их идентичность во всех параллельных цепях.

Требование симметрии подключения касается и цепей управления затворами, где разность в значении индуктивности приводит к различным задержкам момента включения/выключения транзистора. Параметры, непосредственно влияющие на динамические характеристики силовых ключей, также имеют разброс:

- пороговое напряжение отпирания VGE(th);

- задержка времени включения/выключения tdon/tdoff и скорость включения/выключения tr/tf;

- заряд затвора Qg и характеристика затвора VGE = f(Qg);

- переходная характеристика IC = f(VGE).

Рис. 6. Варианты параллельного соединения управляющих входов IGBT

На разброс значения VGE(th) следует обратить особое внимание: достаточно распространенной ошибкой является непосредственное соединение затворов параллельных модулей. Разница в пороговом напряжении отпирания ключей ∆VGE(th) (см. рис. 6б) приводит к тому, что модуль с минимальным значением VGE(th) откроется первым и примет на себя всю токовую нагрузку. Этот эффект усугубляется тем, что напряжение отпирания затвора имеет отрицательный температурный коэффициент. IGBT с большим пороговым напряжением откроется с задержкой ∆t11, определяемой временем включения модуля с меньшим VGE(th). Напомним, что длина горизонтального участка характеристики затвора зависит от значения емкости Миллера «коллектор - затвор» Ccg. Спадающее напряжение на коллекторе дифференцируется этой емкостью и создает ток, компенсирующий ток включения.

Для решения проблемы существует простое и хорошо известное решение: все параллельно соединенные ключи должны иметь индивидуальные и одинаковые резисторы затвора RG. В этом случае напряжение на каждом затворе будет нарастать независимо и разница времени задержки включения не превысит ∆t1, как показано на рисунке 7а.

Рис. 7. Задержка при включении параллельных IGBT: а - при использовании раздельных

резисторов затвора, б - при использовании общего резистора затвора

При соединении затворов, прежде всего, необходимо убедиться в том, что нагрузочные характеристики платы управления позволяют обеспечивать заряд и разряд n параллельно соединенных затворных емкостей. Максимальное значение суммарного заряда затвора нагрузки (n × Qg) должно быть меньше, а эквивалентного резистора затвора (Rg/n) - больше величин, допустимых для драйвера. Среднее значение выходного тока источника питания драйвера Iav должно удовлетворять соотношению:

Iav > n × Qg × fsw,

где fsw - максимальная частота коммутации.

На поведение параллельно включенных модулей в динамических режимах существенное влияние оказывают паразитные индуктивности линий связи и их отличие, вызываемое недостаточной симметрией топологии подключения. Разница напряжений, наводимых на индуктивностях шин (V1...Vn на рис. 6б), приводит к возникновению выравнивающих токов, величина которых практически ничем не ограничена. Одновременно в контурах, образованных индуктивностями шин и емкостями транзисторов, могут возбуждаться паразитные генерации. Для борьбы с этим опасным явлением в сигнальных цепях эмиттеров рекомендуется устанавливать резисторы RE номиналом от 0,5 Ом до 0,1 RG. Наличие этих сопротивлений позволяет ограничить уравнивающие токи значением, не превышающим 10 А, и демпфировать паразитные контуры.

Кроме того, добавление в схему эмиттерных резисторов приводит к образованию отрицательной обратной связи по току, позволяющей нивелировать разницу динамических характеристик силовых ключей. Как показано на рисунке 8, уравнивающий ток i создает падение напряжения VRE на сопротивлениях в сигнальных цепях эмиттеров.

Рис. 8. Компенсация динамических характеристик IGBT

За счет этого происходит частичная компенсация напряжения VGE на затворе «быстрого» IGBT и скорость его включения снижается. Напряжение управления «медленного» транзистора соответственно возрастает, что ускоряет его открывание. При выключении наблюдается обратный эффект, т.о. применение схемы, показанной на рисунке 8б, позволяет выровнять скорость переключения параллельно соединенных модулей IGBT и их динамические потери.

На рисунке 9 приведена схема объединительной печатной платы, устанавливаемой SEMIKRON в большинстве практических реализаций, где используется параллельное соединение модулей.

Рис. 9. Параллельное соединение входов управления IGBT

На схеме показано, как геометрия цепей подключения затворов обеспечивает симметрию относительно входа. В универсальной инверторной платформе SEMIKUBE, разработанной компанией SEMIKRON, для наращивания мощности в параллель соединяется до 8 силовых ключей, объединяемых по затвору с помощью аналогичной схемы. На плате размещаются резисторы затворов RG (раздельные для режимов включения и выключения), эмиттерные сопротивления и диоды-супрессоры. Как было показано выше, такая схема позволяет уровнять динамические характеристики параллельных ключей, а также предотвратить пробой затвора и ограничить ток КЗ. Объединительная плата устанавливается непосредственно на сигнальные выводы модулей, соединение ее входа с выходом драйвера осуществляется бифилярным экранированным кабелем.

Заключение

Проектирование преобразователей высокой мощности является сложнейшей задачей, требующей внимательного подхода на всех этапах проектирования. Успешная разработка подобных изделий немыслима без учета распределенных параметров конструкции и следования ряду стандартных рекомендаций, важность которых подтверждена многолетним опытом.

В предлагаемой статье приведены основные рекомендации по трассировке сигнальных цепей силовых каскадов, без которых невозможно обеспечить надежную работу изделия.

Литература

1. Маркус Хермвиль, Андрей Колпаков «Управление изолированным затвором IGBT. Часть 1 и 2», Новости Электроники ╧11/13, 2008 г.

2. Pramod Bhosale, Markus Hermwille «Connection of Gate Drivers to IGBT and Controller», SEMIKRON Application Note AN 7002, 2006

3. Колпаков А.И. «SEMIX + SKYPER = адаптивный интеллектуальный модуль IGBT», Силовая электроника ╧1, 2005 г.

4. Application Manual Power Modules, SEMIKRON International

5. M. Hermwille, «Plug and Play IGBT Driver Cores for Converters», Power Electronics Europe Issue 2, pp. 10-12, 2006.

Получение технической информации, заказ образцов, поставка -

e-mail: theory.vesti@compel.ru

Журнал "Новости Электроники", номер 15, 2008 год.

Журнал "Новости Электроники", номер 15, 2008 год.